# **Current Mode Boost-Type LED Driver with Programmable Dimming Control**

### **General Description**

The RT8537 is a current mode Boost-type LED driver with programmable brightness dimming control for portable devices. With the 40V integrated MOSFET, the RT8537 can support up to 10 LEDs in series and wide input voltage range from 2.9V to 18V. The Boost converter runs at 1.2MHz switching frequency which allows for the use of small external components.

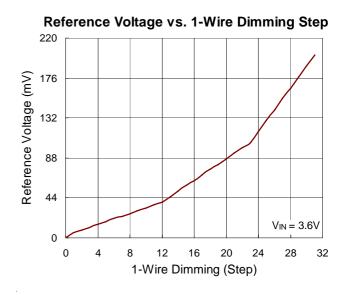

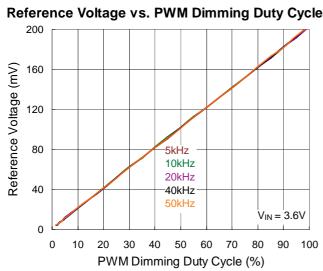

The LED current is adjustable by an external resister at FB pin and the feedback voltage is regulated to 200mV typically. The RT8537 provides PWM dimming mode and 1-wire digital dimming mode for accurate LED current control from EN pin. In PWM dimming mode, the feedback reference voltage is changed with the PWM duty cycle proportionally and the available PWM frequency range is from 5kHz to 50kHz. In 1-wire digital dimming mode, it provides a programmable 32-step brightness dimming function with the EN pin setting.

The RT8537 provides protection functions including LED open protection, input under voltage lockout, current limit and over temperature protection.

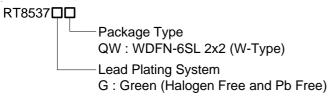

The RT8537 is available in the WDFN-6SL 2x2 package.

### **Features**

- 32-Step Programmable Digital Dimming

- PWM Brightness Dimming

- 2.9V to 18V Input Voltage Range

- 38V Open LED Protection for 10 LEDs

- 200mV Reference with 4% Accuracy

- 1.2MHz Switching Frequency

- Built-In 1.2A Power Switch

- Built-in Internal Soft-Start

- Over Temperature Protection

- Current Limit Protection

- Tiny Package with WDFN Package

- RoHS Compliant and Halogen Free

### **Applications**

- Mobile Phone and Smart Phone

- Digital Camera and GPS

- Portable DVD Player

### **Marking Information**

0J : Product Code W : Date Code

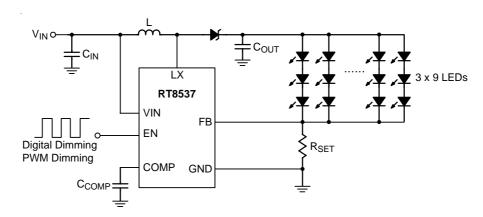

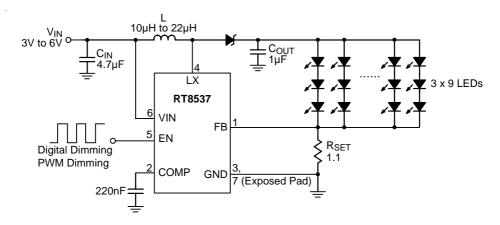

# **Simplified Application Circuit**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Ordering Information**

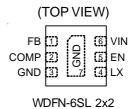

# **Pin Configurations**

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Function Pin Description**

| Pin No.               | Pin Name | Pin Function                                                                                                                         |

|-----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | FB       | Feedback Voltage Input. Connect a resistor between this pin and GND to set the current.                                              |

| 2                     | COMP     | Compensation Node. Connect a suitable capacitor to this pin for stability.                                                           |

| 3,<br>7 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                          |

| 4                     | LX       | Switch Node. Connect the LX pin to the external Inductor. This pin is also used to sense the output voltage for open LED protection. |

| 5                     | EN       | Enable Control Input. This pin can be Used for PWM dimming and 1-wire digital dimming.                                               |

| 6                     | VIN      | Supply Voltage Input.                                                                                                                |

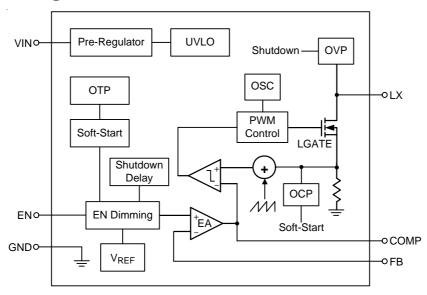

# **Function Block Diagram**

DS8537-00 May 2013

### **Operation**

The RT8537 is a constant frequency, current mode Boosttype LED driver. In normal operation, the N-MOSFET is turned on when the PWM Control circuit is set by the oscillator and is turned off when the current comparator resets the PWM Control circuit. While the N-MOSFET is turned off, the inductor current conducts through the external diode.

### **Pre-Regulator**

The regulator provides low voltage power to supply the internal control circuits.

#### **ULVO**

When the input voltage is lower than the UVLO threshold (2.2V typ.), the driver will turn off. There is a 70mV for the UVLO hysteresis control.

#### Soft-Start

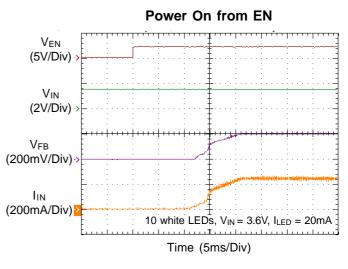

When the device is enabled, the internal  $V_{\text{REF}}$  ramps up to the target voltage in a specific time. This ensures that the output voltage rises slowly to reduce the input inrush current.

### **EN Dimming**

The EN pin is used for the control input for both PWM dimming mode and digital dimming mode. The dimming mode is decided when the device is enabled. The default dimming mode is PWM dimming mode. To enter digital mode, a certain digital pattern on the EN pin must be recognized when the IC starts from shutdown mode.

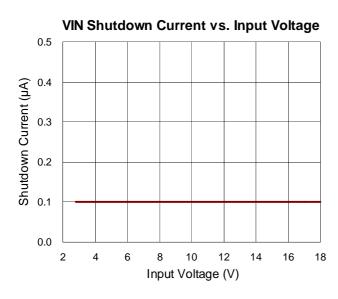

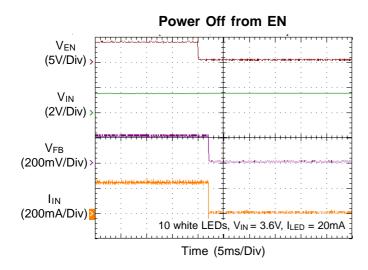

#### **Shutdown Delay**

When the EN voltage is logic low for more than 2.5ms, the driver will be shut down. In shutdown mode, the input supply current for the device is less than  $1\mu$ A.

#### **OCP**

The driver provides cycle-by-cycle current limit function to control the current on power switch.

#### **OVP**

The over voltage protection function monitors the output voltage via LX pin voltage. The OVP threshold voltage is 38V typically. Once the LED is open, the output voltage reaches the OVP threshold, the driver will be shut down.

#### **OTP**

The over temperature protection function will shut down the switching operation when the junction temperature exceeds 160°C. Once the junction temperature cools down by approximately 15°C, the converter will automatically resume switching.

# Absolute Maximum Ratings (Note 1)

| • VIN, EN to GND                                                            | - −0.3V to 20V |

|-----------------------------------------------------------------------------|----------------|

| • FB, COMP to GND                                                           | - −0.3V to 3V  |

| • LX to GND                                                                 | - −0.3V to 40V |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WDFN-6SL 2x2                                                                | · 2.99W        |

| Package Thermal Resistance (Note 2)                                         |                |

| WDFN-6SL 2x2, $\theta_{JA}$                                                 | · 33.5°C/W     |

| • Lead Temperature (Soldering, 10 sec.)                                     | · 260°C        |

| • Junction Temperature                                                      | · 150°C        |

| Storage Temperature Range                                                   | -65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      | · 2kV          |

| MM (Machine Model)                                                          | · 200V         |

|                                                                             |                |

## **Recommended Operating Conditions** (Note 4)

• Supply Input Voltage, VIN ------ 2.9V to 18V

• Junction Temperature Range ----- --- -40°C to 125°C

• Ambient Temperature Range ----- --- -40°C to 85°C

### **Electrical Characteristics**

$(V_{IN} = 3.6V, T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Parame                          | eter                 | Symbol                | Test Conditions                  | Min | Тур | Max | Unit |

|---------------------------------|----------------------|-----------------------|----------------------------------|-----|-----|-----|------|

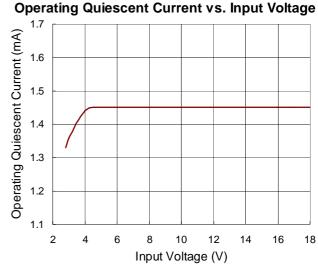

| Operating Quiesce into VIN      | ent Current          | IQ                    | Device PWM Switching No Load     |     |     | 2.3 | mA   |

| Shutdown Current                |                      | I <sub>SHDN</sub>     | EN = GND, V <sub>IN</sub> = 4.2V |     |     | 1   | μΑ   |

| Under Voltage Loc<br>Threshold  | kout                 | V <sub>UVLO</sub>     | V <sub>IN</sub> Falling          |     | 2.2 | 2.5 | V    |

| Under Voltage Loc<br>Hysteresis | kout                 | V <sub>UVLO_Hys</sub> |                                  |     | 70  |     | mV   |

| EN Input Voltage                | Logic-High           | V <sub>IH</sub>       | V <sub>IN</sub> = 2.9V to 18V    | 1.2 |     |     | V    |

| EN Input Voltage                | Logic-Low            | $V_{IL}$              | V <sub>IN</sub> = 2.9V to 18V    |     |     | 0.4 |      |

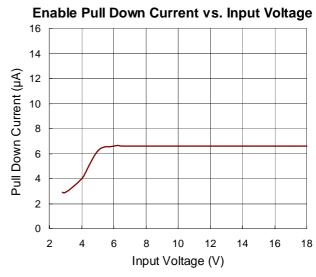

| EN Pull Down Cur                | EN Pull Down Current |                       |                                  |     | 3   | 10  | μΑ   |

| EN Pulse width to               | Shutdown             | toff                  | EN High to Low                   | 2.5 |     |     | ms   |

| Digital Dimming D               | etection Time        | t <sub>ES_Det</sub>   | EN Pin Low                       | 260 |     |     | μS   |

| Digital Dimming D               | etection Delay       | t <sub>ES_Delay</sub> |                                  | 100 |     |     | μS   |

| Digital Dimming Downston        | etection             | t <sub>ES_Win</sub>   | Measured from EN High            | 1   |     |     | ms   |

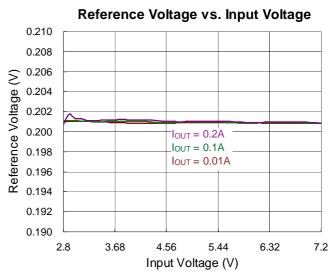

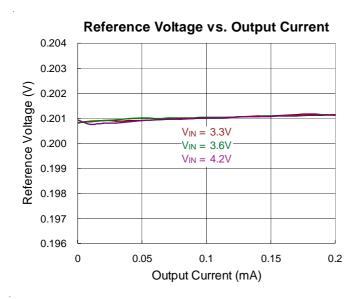

| Feedback Reference Voltage      |                      | $V_{REF}$             |                                  | 192 | 200 | 208 | mV   |

| Feedback Input bia              | as Current           | I <sub>FB</sub>       | V <sub>FB</sub> = 200mV          |     |     | 2   | μΑ   |

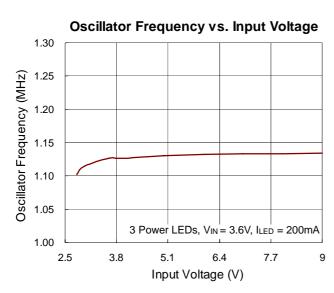

| Oscillator Frequen              | су                   | fosc                  |                                  | 1   | 1.2 | 1.5 | MHz  |

| Maximum Duty Cy                 | cle                  | D <sub>MAX</sub>      |                                  | 90  | 93  |     | %    |

| Parameter                        | Symbol               | Test Conditions                  | Min                   | Тур  | Max  | Unit |

|----------------------------------|----------------------|----------------------------------|-----------------------|------|------|------|

| Minimum On Pulse Width           | t <sub>MIM_ON</sub>  |                                  |                       | 40   |      | ns   |

| COMP Pin Sink Current            | I <sub>Sink</sub>    |                                  |                       | 60   |      | μΑ   |

| COMP Pin Source Current          | I <sub>Source</sub>  |                                  |                       | 60   |      | μΑ   |

| Error Amplifier transconductance | G <sub>EA</sub>      |                                  | 240                   | 320  | 400  | μΑ/V |

| N-MOSFET On-Resistance           | R <sub>DS(ON)</sub>  | V <sub>IN</sub> = 3V             |                       | 0.35 | 0.7  | Ω    |

| N-MOSFET Leakage Current         | I <sub>LN_NFET</sub> | V <sub>LX</sub> = 35V, EN = Low  |                       | -    | 1    | μΑ   |

| N-MOSFET Current Limit           | I <sub>LIM</sub>     |                                  | 0.96                  | 1.2  | 1.44 | Α    |

| Open LED Protection<br>Threshold | V <sub>OVP</sub>     | Measured on the LX pin, L = 22μH | 37                    | 1    | 42   | ٧    |

| Start Time of Program Stream     | t <sub>Start</sub>   |                                  | 3                     | ŀ    |      | μS   |

| End Time of Program Stream       | t <sub>EOS</sub>     |                                  | 3                     | -    | 360  | μS   |

| High Time Low Bit                | t <sub>H_LB</sub>    | Logic 0                          | 3                     | 1    | 180  | μS   |

| Low Time Low Bit                 | t <sub>L_LB</sub>    | Logic 0                          | 2 x t <sub>H_LB</sub> | ŀ    | 360  | μS   |

| High Time High Bit               | t <sub>H_HB</sub>    | Logic 1                          | 2 x t <sub>L_HB</sub> | -    | 360  | μS   |

| Low Time High Bit                | t <sub>L_HB</sub>    | Logic 1                          | 3                     |      | 180  | μS   |

| Thermal Shutdown Threshold       | T <sub>SD</sub>      |                                  |                       | 160  |      | °C   |

| Thermal Shutdown Hysteresis      | ΔT <sub>SD</sub>     |                                  |                       | 15   |      | °C   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25$ °C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. The reference voltage accuracy is  $\pm 2.5\%$  at recommended ambient temperature range, guaranteed by design.

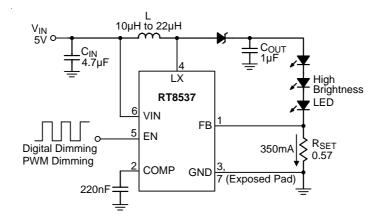

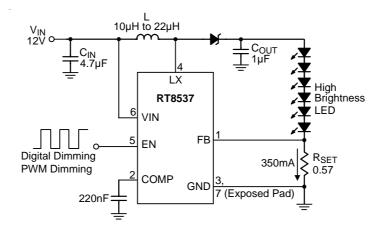

# **Typical Application Circuit**

Figure 1. Drive 27 LEDs for Media form Factor Display

Figure 2. Application Circuit for 3 High Brightness LEDs

Figure 3. Application Circuit for 6 High Brightness LEDs

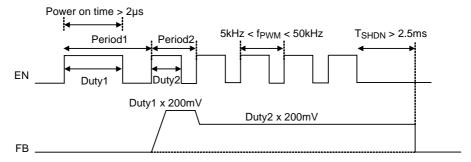

## **Timing Diagram**

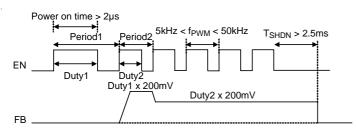

### **PWM Dimming Mode**

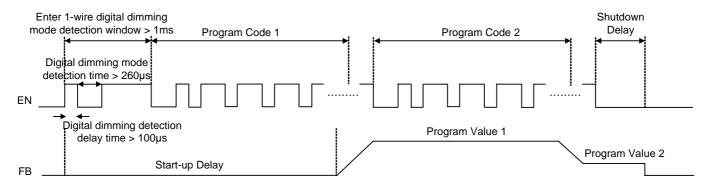

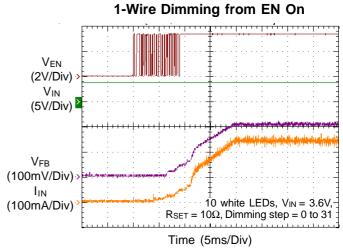

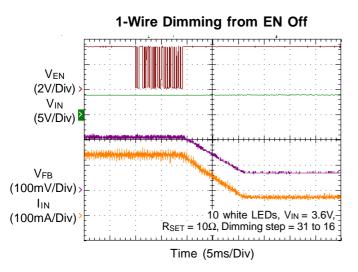

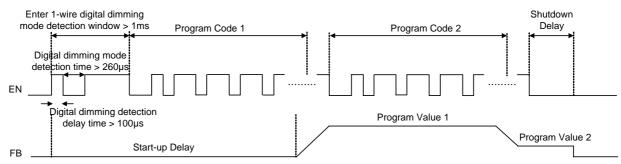

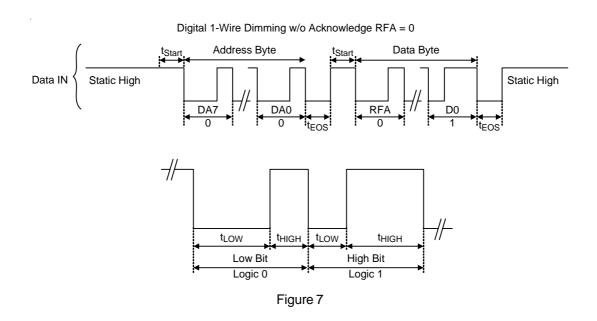

### 1-Wire Digital Dimming Mode

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

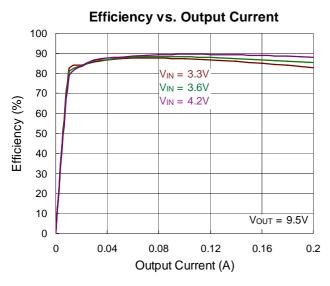

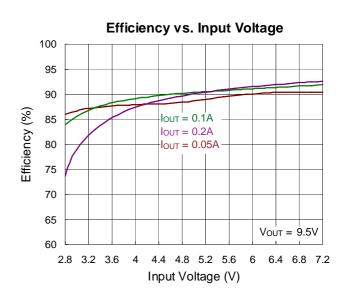

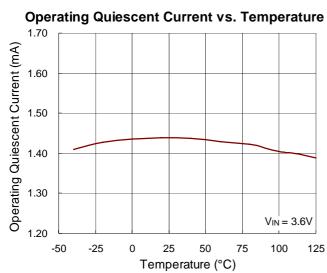

# **Typical Operating Characteristics**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Application Information**

#### Soft-Start

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is enabled, the  $V_{\text{REF}}$  ramps up slowly to the target voltage within a specific time. This ensures that the output voltage rises slowly to reduce the input current.

### **Open LED Protection**

Open LED protection circuitry prevents IC from damage as the result of LED disconnection. The RT8537 monitors the voltage at the LX pin during each switching cycle. The circuitry turns off the switch and shuts down the IC as soon as the LX voltage exceeds the  $V_{\text{OVP}}$  threshold (38V typ.). The device remains in shutdown mode until it is enabled by toggling the EN pin logic.

#### **Shutdown**

The RT8537 enters shutdown mode when the EN pin is pulled low for 2.5ms. During shutdown, the input supply current for the device is less than  $1\mu A$ . Although the internal FET does not switch in shutdown, there is still a DC current path between the input and the LEDs through the inductor and Schottky diode. The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown.

#### **Current Setting**

The LED current is adjustable by an external current sense resistor in series with the LED string. The LED current can be calculated by the following equation:

$$I_{LED} = \frac{V_{REF}}{R_{SET}}$$

#### Where:

I<sub>LED</sub> = output current of LEDs

V<sub>REF</sub> = feedback reference voltage (200mV typ.)

R<sub>SET</sub> = current sense resistor

The output current tolerance depends on the  $V_{\text{REF}}$  accuracy and the current sense resistor accuracy.

### **LED Brightness Dimming Mode Selection**

The EN pin is used for the control input for both dimming modes, PWM dimming mode and 1-wire digital dimming mode. The dimming mode for the RT8537 is selected when the device is enabled. The default dimming mode is PWM dimming mode. To enter digital dimming mode, the following digital pattern on the EN pin must be recognized by the IC when the IC starts from the shutdown mode.

- Pull the EN pin high to enable the RT8537 and start the detection window (t<sub>ES win</sub>, 1ms) for digital dimming

- After the digital dimming detection delay time (t<sub>ES\_Delay</sub>, 100μs), drive the EN low for more than the detection time (t<sub>ES\_Detect</sub>, 260μs).

- Pull the EN pin high after the detection time (260μs) and before the detection window (t<sub>ES\_Win</sub>, 1ms), once the above 3 conditions are met, the IC immediately enters the digital 1-wire dimming mode. The digital dimming communication can start before the detection window expires. Once the dimming mode is selected, it can not be changed without another start up. This means the IC needs to be shut down by pulling the EN low for 2.5ms and restarts. See the dimming mode detection and soft-start (see Figure 4) for a graphical explanation.

Figure 4. Start-Up for Digital Dimming Mode

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

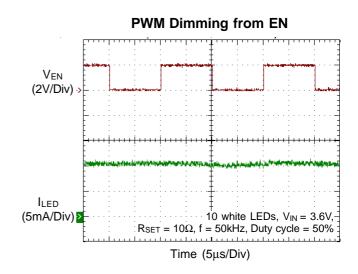

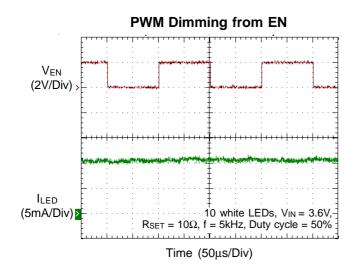

#### **PWM Dimming Mode**

When the EN pin is constantly high, the FB voltage is regulated to 200mV typically. However, the EN pin allows a PWM signal to reduce this regulation voltage; therefore, it achieves LED brightness dimming. The relationship between the duty cycle and FB voltage is given by

$V_{FB} = Duty \times V_{REF}$

Where:

Duty = duty cycle of the PWM signal

V<sub>REF</sub> = internal reference voltage (200mV typ.)

The RT8537 chops up the internal 200mV reference voltage at the duty cycle of the PWM signal. Therefore, although a PWM signal is used for brightness dimming, only the LED DC current is modulated, which is often referred as analog dimming. This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control.

For optimum performance, use the PWM dimming frequency in the range of 5kHz to 50kHz. The requirement of minimum dimming frequency comes from the digital dimming detection delay and detection time specification in the dimming mode selection.

Figure 5. PWM Dimming Control

#### 1-Wire Digital Dimming Mode

The RT8537 adopts an 1-wire digital protocol for the digital dimming mode control, which can program the FB voltage to any of the 32 steps with single command. The step increment increases with the voltage to produce pseudo logarithmic curve for the brightness step. See Table 1 for the FB pin voltage steps. The default step is full scale when the device is first enabled (V<sub>FB</sub> = 200mV). The

programmed reference voltage is stored in an internal register. A power reset clears the register value and resets it to default. It is recommended to finish the first address/ data stream before 2ms at C<sub>COMP</sub> = 220nF during start-up for the 1-wire dimming, to avoid the possibilities for LED brightness changes from bright to dark. Especially the digital dimming code is below step 5 ( $V_{FB} = 17 \text{mV}$ ).

The digital dimming interface is based on a master slave structure, where the master is typically a microcontroller or application processor. Figure 6 and Table 2 give an overview of the protocol. The protocol consists of a device specific address byte and a data byte. The device specific address byte is fixed to 72 hex. The data byte consists of five bits for information, two address bits, and the RFA bit always set to 0. The advantage of 1-wire digital dimming compared with other one pin interfaces is that its bit detection is in a large extent independent from the bit transmission rate. It can automatically detect bit rates between 1.7kBit/sec and up to 160kBit/sec.

All bits are transmitted MSB first and LSB last. Figure 7 shows the protocol without acknowledge request (Bit RFA = 0). Prior to both bytes, device address byte and data byte, a start condition must be applied. For this, the EN pin must be pulled high for at least t<sub>Start</sub> (3µs) before the bit transmission starts with the falling edge. If the EN pin is already at a high level, no start condition is needed prior to the device address byte. The transmission of each byte is closed with an end of stream condition for at least  $t_{EOS}$  (3 $\mu$ s).

The bit detection is based on a logic detection scheme, where the criterion is the relation between t<sub>LOW</sub> and t<sub>HIGH</sub>. It can be simplified to:

High Bit: t<sub>HIGH</sub> > t<sub>LOW</sub>, but with t<sub>HIGH</sub> at least 2 x t<sub>LOW</sub>, see Figure 7.

Low Bit: t<sub>HIGH</sub> < t<sub>LOW</sub>, but with t<sub>LOW</sub> at least 2 x t<sub>HIGH</sub>, see Figure 7.

The bit detection starts with a falling edge on the EN pin and ends with the next falling edge. Depending on the relation between t<sub>HIGH</sub> and t<sub>LOW</sub>, the logic 0 or 1 is detected.

Table 1. 32-Step Digital Dimming Setting

| Step | FB Voltage<br>(mV) | D4 | D3 | D2 | D1 | D0 |

|------|--------------------|----|----|----|----|----|

| 0    | 0                  | 0  | 0  | 0  | 0  | 0  |

| 1    | 5                  | 0  | 0  | 0  | 0  | 1  |

| 2    | 8                  | 0  | 0  | 0  | 1  | 0  |

| 3    | 11                 | 0  | 0  | 0  | 1  | 1  |

| 4    | 14                 | 0  | 0  | 1  | 0  | 0  |

| 5    | 17                 | 0  | 0  | 1  | 0  | 1  |

| 6    | 20                 | 0  | 0  | 1  | 1  | 0  |

| 7    | 23                 | 0  | 0  | 1  | 1  | 1  |

| 8    | 26                 | 0  | 1  | 0  | 0  | 0  |

| 9    | 29                 | 0  | 1  | 0  | 0  | 1  |

| 10   | 32                 | 0  | 1  | 0  | 1  | 0  |

| 11   | 35                 | 0  | 1  | 0  | 1  | 1  |

| 12   | 38                 | 0  | 1  | 1  | 0  | 0  |

| 13   | 44                 | 0  | 1  | 1  | 0  | 1  |

| 14   | 50                 | 0  | 1  | 1  | 1  | 0  |

| 15   | 56                 | 0  | 1  | 1  | 1  | 1  |

| Step | FB Voltage (mV) | D4 | D3 | D2 | D1 | D0 |

|------|-----------------|----|----|----|----|----|

| 16   | 62              | 1  | 0  | 0  | 0  | 0  |

| 17   | 68              | 1  | 0  | 0  | 0  | 1  |

| 18   | 74              | 1  | 0  | 0  | 1  | 0  |

| 19   | 80              | 1  | 0  | 0  | 1  | 1  |

| 20   | 86              | 1  | 0  | 1  | 0  | 0  |

| 21   | 92              | 1  | 0  | 1  | 0  | 1  |

| 22   | 98              | 1  | 0  | 1  | 1  | 0  |

| 23   | 104             | 1  | 0  | 1  | 1  | 1  |

| 24   | 116             | 1  | 1  | 0  | 0  | 0  |

| 25   | 128             | 1  | 1  | 0  | 0  | 1  |

| 26   | 140             | 1  | 1  | 0  | 1  | 0  |

| 27   | 152             | 1  | 1  | 0  | 1  | 1  |

| 28   | 164             | 1  | 1  | 1  | 0  | 0  |

| 29   | 176             | 1  | 1  | 1  | 0  | 1  |

| 30   | 188             | 1  | 1  | 1  | 1  | 0  |

| 31   | 200             | 1  | 1  | 1  | 1  | 1  |

| Data  | Data IN Device Address |          |          |          |          |          |          | Data Byte |     |       |          |         |         |    |    |    |    |    |     |

|-------|------------------------|----------|----------|----------|----------|----------|----------|-----------|-----|-------|----------|---------|---------|----|----|----|----|----|-----|

| Start | DA7<br>0               | DA6<br>1 | DA5<br>1 | DA4<br>1 | DA3<br>0 | DA2<br>0 | DA1<br>1 | DA0<br>0  | EOS | Start | RFA<br>0 | A1<br>0 | A0<br>0 | D4 | D3 | D2 | D1 | D0 | EOS |

Data OUT

Figure 6

Table 2.

| Byte              | Bit<br>Number | Name | Transmission<br>Description | Description          |

|-------------------|---------------|------|-----------------------------|----------------------|

|                   | 7             | DA7  |                             | 0 MSB device address |

|                   | 6             | DA6  |                             | 1                    |

|                   | 5             | DA5  |                             | 1                    |

| Device<br>Address | 4             | DA4  | IN                          | 1                    |

| Byte 72 hex       | 3             | DA3  | IIN                         | 0                    |

|                   | 2             | DA2  |                             | 0                    |

|                   | 1             | DA1  |                             | 1                    |

|                   | 0             | DA0  |                             | 0 LSB device address |

|                   | 7 (MSB)       | RFA  |                             | RFA = 0              |

|                   | 6             | A1   |                             | Address bit 1 = 0    |

|                   | 5             | A0   |                             | Address bit 0 = 0    |

| Data Di ta        | 4             | D4   | IN                          | Data bit 4           |

| Data Byte         | 3             | D3   | IIN                         | Data bit 3           |

|                   | 2             | D2   |                             | Data bit 2           |

|                   | 1             | D1   |                             | Data bit 1           |

|                   | 0 (LSB)       | D0   |                             | Data bit 0           |

#### **Inductor Selection**

The recommended value of inductor for 10 LEDs or high brightness LED applications is from 10µH to 22µH. Smaller size and better efficiency are the major concerns for portable devices. The inductor should have low core loss at 1MHz (Min.) and low DCR for better efficiency. The inductor saturation current rating should be considered to cover the inductor peak current.

### **Capacitor Selection**

For low ripple voltage, ceramic capacitors with low ESR are recommended. X5R and X7R types are suitable because of their wide voltage range and good operating temperature characteristics. For the application of the RT8537 to drive 10 LEDs in series, a 4.7µF for input capacitor, an 1µF for output capacitor and a 220nF for compensation capacitor are recommended.

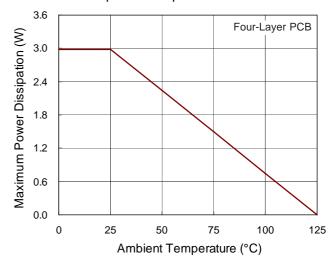

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

DS8537-00 May 2013

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-6SL 2x2 package, the thermal resistance,  $\theta_{JA}$ , is 33.5°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$ can be calculated by the following formula:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (33.5^{\circ}C/W) = 2.99W$  for WDFN-6SL 2x2 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 8 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 8. Derating Curve of Maximum Power Dissipation

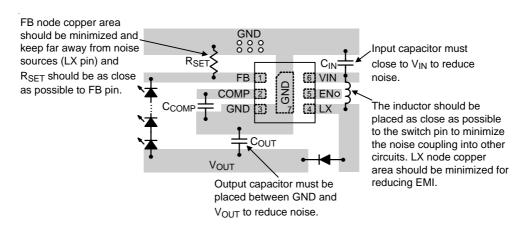

### **Layout Consideration**

For best performance of the RT8537, the following layout guidelines must be strictly followed.

- Input and output capacitors should be connected to a strong ground plane for heat sinking and noise protection.

- Keep the main current traces as possible as short and wide.

- LX node of DC/DC converter is with high frequency voltage swing. It should be kept at a small area.

- Place the feedback components as close as possible to the IC and keep away from the noisy devices.

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

Figure 9. PCB Layout Guide

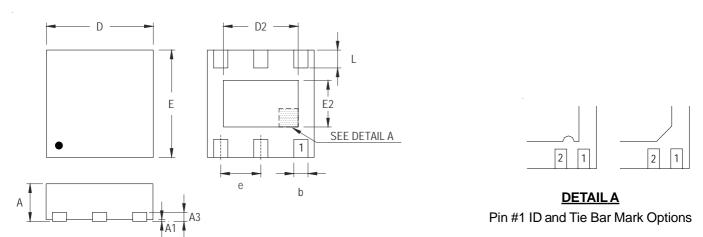

### **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Complete | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |

|----------|------------|----------------|----------------------|-------|--|--|

| Symbol   | Min        | Max            | Min                  | Max   |  |  |

| А        | 0.700      | 0.800          | 0.028                | 0.031 |  |  |

| A1       | 0.000      | 0.050          | 0.000                | 0.002 |  |  |

| A3       | 0.175      | 0.250          | 0.007                | 0.010 |  |  |

| b        | 0.200      | 0.350          | 0.008                | 0.014 |  |  |

| D        | 1.900      | 2.100          | 0.075                | 0.083 |  |  |

| D2       | 1.550      | 1.650          | 0.061                | 0.065 |  |  |

| Е        | 1.900      | 2.100          | 0.075                | 0.083 |  |  |

| E2       | 0.950      | 1.050          | 0.037                | 0.041 |  |  |

| е        | 0.6        | S50            | 0.0                  | 26    |  |  |

| L        | 0.200      | 0.300          | 0.008                | 0.012 |  |  |

W-Type 6SL DFN 2x2 Package

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.