#### PRELIMINARY DATA SHEET

# Si82Fx Isolated Gate Driver with SelVCD<sup>™</sup>, Miller Clamp, and Low Channel-to-Channel Skew

The Si82Fx combines two isolated gate drivers into a single package for high-power applications. The Si82Fx includes devices with single or dual control inputs with independent or high-side/low-side outputs. These drivers can operate with a 3 V to 20 V input supply and a maximum gate driver supply voltage of 30 V. The inputs are CMOS, which provides robust noise margin.

The Si82Fx is ideal for driving power silicon MOSFETs, IGBTs, SiC FETs, and GaN FETs used in various switched power and motor control applications. These drivers utilize Skyworks' proprietary silicon isolation technology, supporting up to 6 kV<sub>RMS</sub> for 1-minute isolation voltage. This technology enables high CMTI (200 kV/ $\mu$ s), lower propagation delays and skew, little variation with temperature and age, and tight part-to-part matching. The Si82Fx family offers longer service life and higher reliability than optocoupled gate drivers.

The output stage features Selectable Variable Current Drive (SelVCD<sup>™</sup>) technology that adjusts output current between eight selectable levels, eliminating the need for gate resistors and clamping any Miller effect currents. SelVCD<sup>™</sup> operates as a current source that maintains current output within a tight tolerance of the target across all operating conditions. The driver family also offers features such as Undervoltage Lockout (UVLO), dead time programmability, and defined output states in all operating conditions.

Automotive Grade is available. These products are built using automotive-specific flows at all steps in the manufacturing process to ensure the robustness and low defectivity required for automotive applications.

# **Applications**

- Isolated switched-mode supplies

- Motor drives

- Power inverters

- Uninterruptable power supplies

- Onboard chargers

- DC-DC converters

# Safety Regulator Approvals (Pending)

- UL 1577 recognized

- Up to 6000  $V_{RMS}$  for one minute

- CSA certification conformity

- 62368-1 (reinforced insulation)

- 60601-1 (2 MOPP)

- VDE certification conformity

- 60747-17 (reinforced insulation)

- CQC certification approval - GB4943.1

# **Key Features**

- Wide input range of 3 to 20 V

- Wide gate supply voltage of 5 to 30 V

- CMOS input with an optional deglitch filter

- Channel-to-channel skew < 5 ns

- Dead time control and overlap protection

- Universal and High-Side/Low-Side pinouts

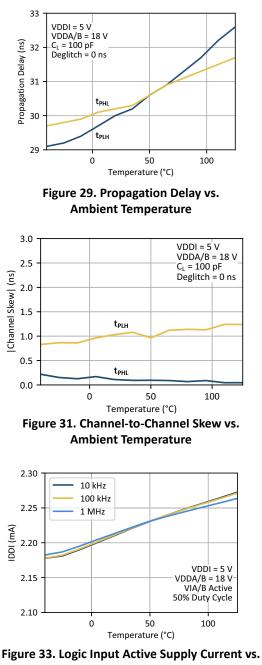

- Selectable Variable Current Drive (SelVCD<sup>™</sup>)

- Integrated Miller clamp

- High precision current source output

- CMTI > 200 kV/μs

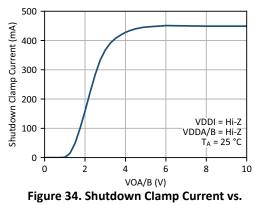

- 1500 V<sub>RMS</sub> working voltage

- Optimized UVLO of 4 V, 8 V, 12 V, or 15 V

- 4 kV HBM ESD rating

- No unknown output states

- Increased channel-to-channel creepage

- 6 kV<sub>RMS</sub> safety rated isolation

- 10 kV bipolar surge

- Wide temperature range: -40 to 125 °C

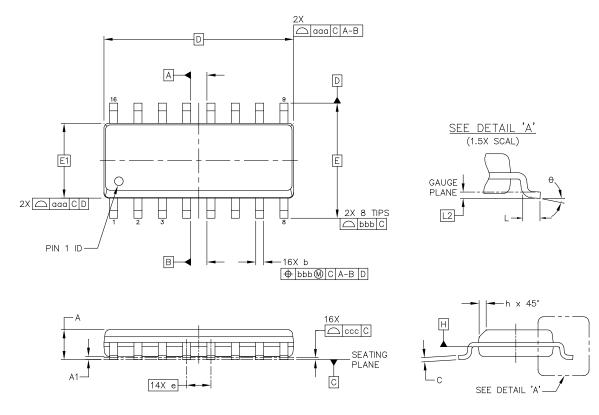

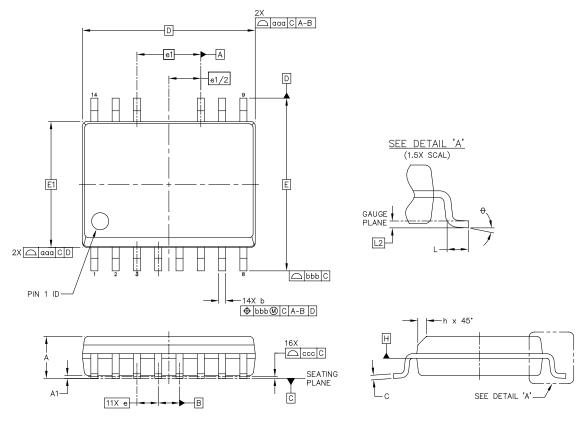

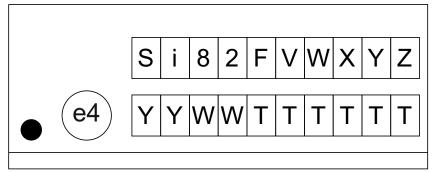

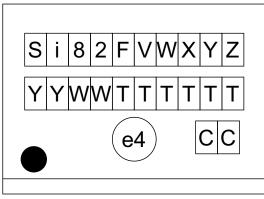

- Narrow-body 16-pin SOIC and wide-body 14-pin SOIC packages

- AEC-Q100 qualification

- Automotive-grade OPNs available

Skyworks Green<sup>™</sup> products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green*<sup>™</sup>, document number SQ04–0074.

# **1. Pin Descriptions**

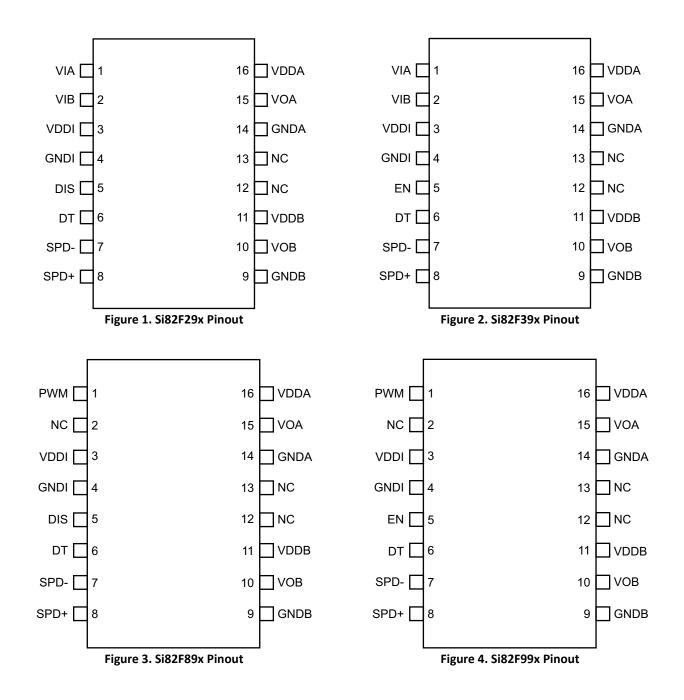

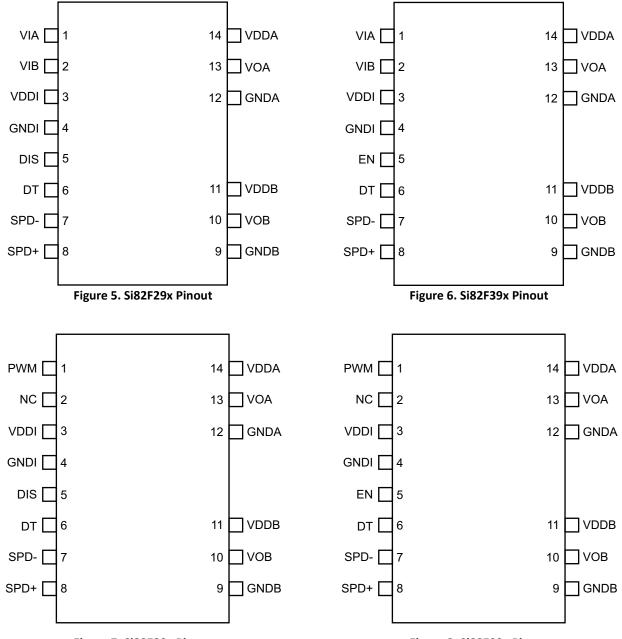

#### **1.1. Device Pinouts**

The Si82Fx consists of multiple dies in packages with different bond-outs for different customer needs. Each bond-out corresponds to a pin-out below. See "10. Ordering Guide" on page 55 for the part numbers and features of these products.

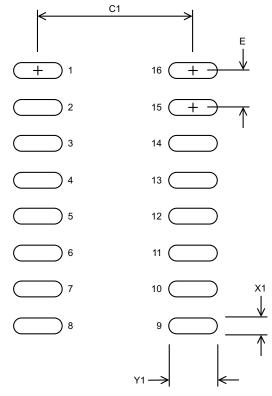

#### 1.1.1. NB SOIC-16 Pinouts

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com 206821A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice

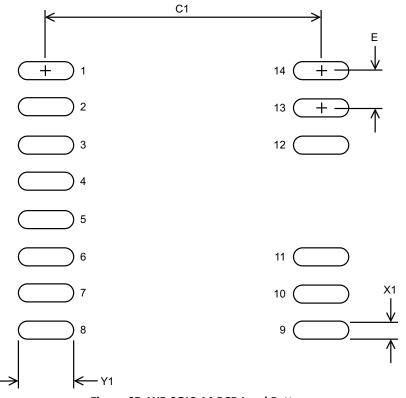

#### 1.1.2. WB SOIC-14 Pinouts

Figure 7. Si82F89x Pinout

Figure 8. Si82F99x Pinout

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com 206821A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice

# 1.2. Pin Details

| Pin Name | Pin Description                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDI     | Logic input power supply.                                                                                                                                                                                                                                                                                                                                                                     |

| GNDI     | Logic input ground terminal.                                                                                                                                                                                                                                                                                                                                                                  |

| PWM      | PWM logic input for gate driver A and gate driver B.                                                                                                                                                                                                                                                                                                                                          |

| VIA      | Non-inverting logic input terminal for gate driver A.                                                                                                                                                                                                                                                                                                                                         |

| VIB      | Non-inverting logic input terminal for gate driver B.                                                                                                                                                                                                                                                                                                                                         |

| EN       | Active high device ENABLE signal. When asserted (logic high), the device is enabled to perform in normal operating mode.<br>When deasserted (logic low), this input unconditionally drives the output VOA and VOB logic low.                                                                                                                                                                  |

| DIS      | Active high device DISABLE signal. When asserted (logic high), this input unconditionally drives the output VOA and VOB logic low. When deasserted (logic low), the device is enabled to perform in normal operating mode.                                                                                                                                                                    |

| DT       | Dead time programming input. The value of the resistor connected from DT to GNDI sets the dead time between output transitions of VOA and VOB. Connecting DT to VDDI will disable dead time insertion on High-Side/Low-Side drivers. Connecting DT to VDDI will disable dead time insertion and overlap protection on Universal drivers.                                                      |

| SPD+     | Driver strength programming input for sourcing current of driver A and driver B. The value of the resistor connected from SPD+ to GNDI sets the controlled sourcing current of the drivers. Connect SPD+ to GNDI to set the controlled sourcing current of the drivers to its minimal value. Connect SPD+ to VDDI to set the controlled sourcing current of the drivers to its maximal value. |

| SPD-     | Driver strength programming input for sinking current of driver A and driver B. The value of the resistor connected from SPD– to GNDI sets the controlled sinking current of the drivers. Connect SPD– to GNDI to set the controlled sinking current of the drivers to its minimal value. Connect SPD– to VDDI to set the controlled sinking current of the drivers to its minimal value.     |

| VDDA     | Gate driver A power supply.                                                                                                                                                                                                                                                                                                                                                                   |

| GNDA     | Gate driver A ground terminal.                                                                                                                                                                                                                                                                                                                                                                |

| VDDB     | Gate driver B power supply.                                                                                                                                                                                                                                                                                                                                                                   |

| GNDB     | Gate driver B ground terminal.                                                                                                                                                                                                                                                                                                                                                                |

| VOA      | Gate driver A output.                                                                                                                                                                                                                                                                                                                                                                         |

| VOB      | Gate driver B output.                                                                                                                                                                                                                                                                                                                                                                         |

| NC       | No connection. The user should not connect anything to this pin.                                                                                                                                                                                                                                                                                                                              |

#### Table 1. Si82Fx Pin Details

## 2. Device Overview

The Si82Fx is an isolated two-channel gate driver available in a Universal or High-Side/Low-Side configuration. Each configuration can be purchased with either an asynchronous enable or disable input. Additional features such as undervoltage lockout (UVLO) level and deglitch filter time can be configured through device selection. Refer to "10. Ordering Guide" on page 55 for more details. Safety-rated isolation is provided from logic input to gate driver output by a pair of high-voltage silicon dioxide (SO<sub>2</sub>) capacitors. These capacitors are duplicated to form a differential path for signals modulated with an RF carrier and using an on-off keying (OOK) modulation scheme. This approach optimizes for fault tolerance and timing performance between input and output.

The digital logic inputs are high-voltage capable, CMOS-compatible, Schmitt triggered, and deglitched for high noise immunity and a wide range of compatibility. See "4.4. Logic Input Signals" on page 12 for more details. Devices with a dead time input will operate as a High-Side/Low-Side driver for half-bridge circuits, inserting dead time between the two output channels and preventing shoot-through current. Additionally, for devices with a universal configuration, the dead time input can be connected to the VDDI supply to disable dead time insertion and overlap protection, enabling the device to operate as a dual driver. See "4.5. Dead Time Control and Overlap Protection" on page 13 for more information. The analog speed control inputs (SPD±) are also high-voltage tolerant and include a high-voltage clamp to protect the device's internal low-voltage circuits. The gate driver outputs operate as a current source. Output current is selectable between eight different levels, eliminating the need for gate resistors and enabling a built-in Miller clamp to operate directly on the gate driver output (VOA/B). See "4.6. Selectable Variable Current Drive (SelVCD<sup>™</sup>)" on page 15 for more information.

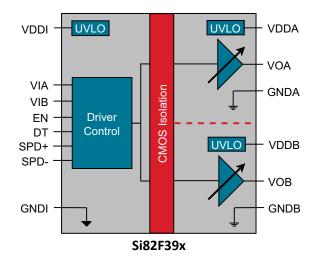

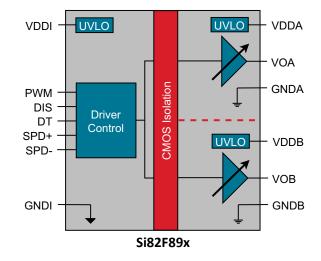

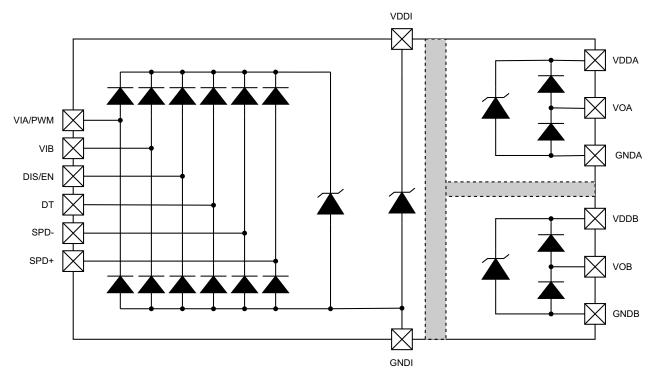

# 3. Functional Block Diagrams

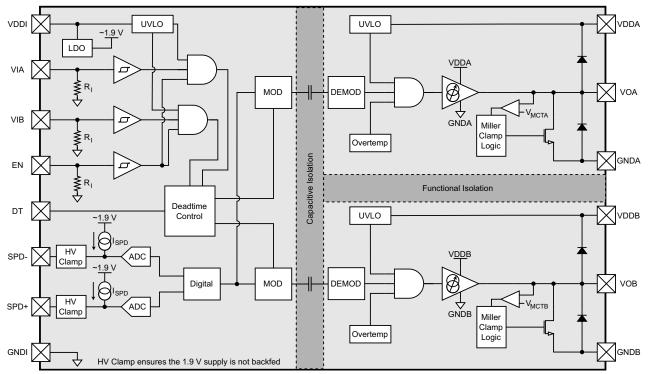

Figure 9. Si82F39x Device with Universal Configuration and Enable Input

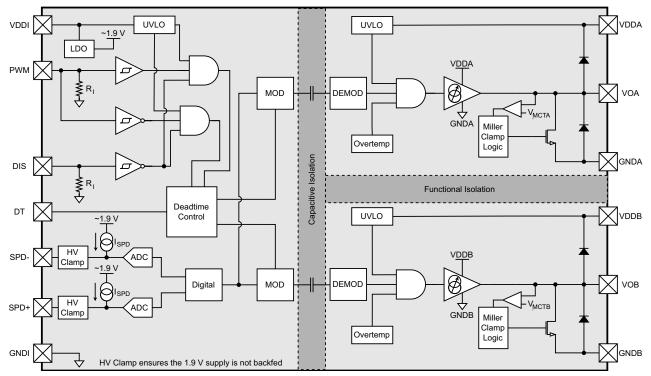

Figure 10. Si82F29x Device with Universal Configuration and Disable Input

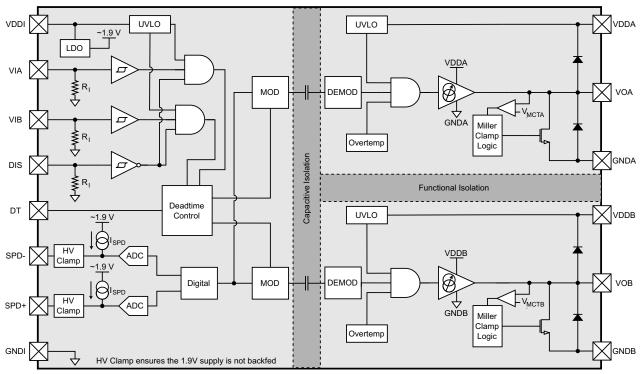

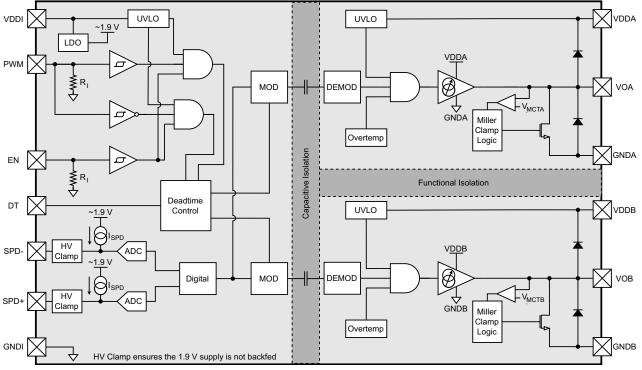

Figure 11. Si82F99x Device with High-Side/Low-Side Configuration and Enable Input

Figure 12. Si82F89x Device with High-Side/Low-Side Configuration and Disable Input

# 4. Device Operation

This section describes the capabilities of the device and how it should be used to achieve different goals within a design. Refer to "5.1. Recommended Application Circuits" on page 19 and "10. Ordering Guide" on page 55 for information on how to best utilize each device for different applications.

## 4.1. Truth Tables

The following tables describe the logical behavior of the Si82Fx Isolated Gate Driver devices.

|     | Inputs <sup>1</sup> |        | Power Supply State <sup>2</sup> |                   |                   | Outputs <sup>3</sup> |                  |  |

|-----|---------------------|--------|---------------------------------|-------------------|-------------------|----------------------|------------------|--|

| VIA | VIB                 | DIS/EN | VDDI <sup>4</sup>               | VDDA <sup>5</sup> | VDDB <sup>5</sup> | VOA                  | VOB              |  |

| Н   | L                   | E      | Р                               | Р                 | _                 | Н                    | L                |  |

| L   | н                   | E      | Р                               | —                 | Р                 | L                    | н                |  |

| Н   | Н                   | E      | Р                               | Р                 | Р                 | H/L <sup>6</sup>     | H/L <sup>6</sup> |  |

| L   | L                   | Х      | _                               | _                 | _                 | L                    | L                |  |

| x   | х                   | D      | _                               | _                 | _                 | L                    | L                |  |

| х   | Х                   | Х      | NP                              | _                 | _                 | L                    | L                |  |

| L   | Х                   | Х      | Р                               | _                 | NP                | L                    | L                |  |

| н   | Н                   | E      | Р                               | Р                 | NP                | H/L <sup>6</sup>     | L                |  |

| Х   | L                   | Х      | Р                               | NP                | —                 | L                    | L                |  |

| Н   | Н                   | E      | Р                               | NP                | Р                 | L                    | H/L <sup>6</sup> |  |

Table 2. Si82F2x-3x Truth Table

1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. "E" indicates the driver is enabled (DIS = L or EN = H), "D" indicates the driver is disabled (DIS = H or EN = L). Input pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the power supply state.

"NP" is the "not powered" state; "P" is the "powered" state, and "-" is an irrelevant state.

3. "H" is a logic high (true) value, and "L" is a logic low (false). The logic low (L) value is enforced by the Shutdown Clamp (see "4.9. Shutdown Clamp" on page 17) if the same side gate driver's power supply (VDDA/B) is not powered (NP).

"Not powered" (NP) state is defined as VDDI < VDDI<sub>UV</sub>. "Powered" (P) state is defined as VDDI > VDDI<sub>UV</sub>.

"Not powered" (NP) state is defined as VDDA/B<sub>UV</sub>. "Powered" (P) state is defined as VDDA/B<sub>UV</sub>.

The output state depends on the dead time pin (DT). If the dead time pin is connected to VDDI, the output will be a logic high (H). If the dead time pin is not connected to VDDI, the output will be a logic low (L). See "4.5. Dead Time Control and Overlap Protection" on page 13 for more information.

| Inp | outs <sup>1</sup> | Power Supply State <sup>2</sup> |                   |                   | Outp | outs <sup>3</sup> |

|-----|-------------------|---------------------------------|-------------------|-------------------|------|-------------------|

| PWM | DIS/EN            | VDDI <sup>4</sup>               | VDDA <sup>5</sup> | VDDB <sup>5</sup> | VOA  | VOB               |

| Н   | E                 | Р                               | Р                 | -                 | н    | L                 |

| L   | E                 | Р                               | _                 | Р                 | L    | Н                 |

| Х   | D                 | Р                               | _                 | _                 | L    | L                 |

| Х   | х                 | NP                              | _                 | _                 | L    | L                 |

| Н   | E                 | Р                               | Р                 | NP                | Н    | L                 |

| L   | E                 | Р                               | _                 | NP                | L    | L                 |

| Н   | E                 | Р                               | NP                | _                 | L    | L                 |

| L   | E                 | Р                               | NP                | Р                 | L    | Н                 |

#### Table 3. Si82F8x-9x Truth Table

1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. "E" indicates the driver is enabled (DIS = L or EN = H), "D" indicates the driver is disabled (DIS = H or EN = L). Input pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the power supply state.

"NP" is the "not powered" state; "P" is the "powered" state, and "—" is an irrelevant state.

"H" is a logic high (true) value, and "L" is a logic low (false). The logic low (L) value is enforced by the Shutdown Clamp (see "4.9. Shutdown Clamp" on page 17) if the same Side gate driver's supply (VDDA/B) is not powered (NP).

"Not powered" (NP) state is defined as VDDI < VDDI<sub>UV</sub>. "Powered" (P) state is defined as VDDI > VDDI<sub>UV</sub>.

"Not powered" (NP) state is defined as VDDA/B < VDDA/B<sub>UV</sub>. "Powered" (P) state is defined as VDDA/B > VDDA/B<sub>UV</sub>.

#### 4.2. Power Sequence and Timing Behavior

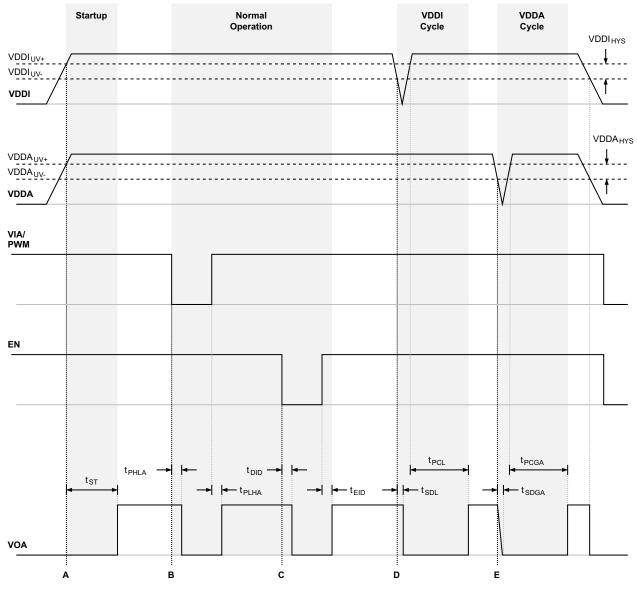

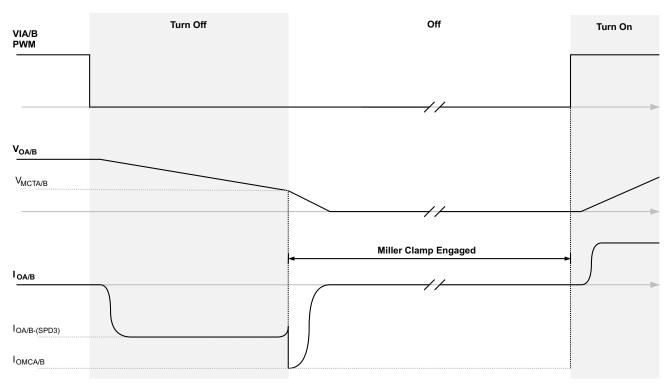

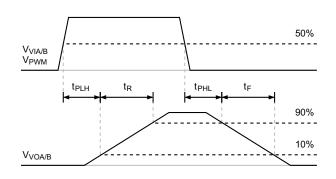

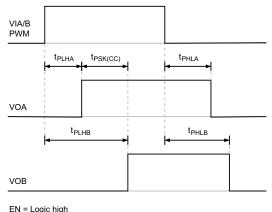

The device exhibits different timing behavior depending on the state of the power supplies as well as the driver inputs. Figure 13, "Gate Driver Timing Behavior," below shows how the analog power supply voltages are plotted against the digital input and output state of the device, with relevant device timings listed.

#### Figure 13. Gate Driver Timing Behavior

Note that this diagram shows the timing relationship between VDDA, VIA/PWM and VOA. However, the same timing relationship applies for VDDB, VIB and VOB.

# 4.3. Undervoltage Lockout

Undervoltage Lockout (UVLO) is provided to prevent erroneous operation during device startup and shutdown or when VDDI or VDDA/B is below its specified operating circuits range. The power supplies associated with the logic input, gate driver A, and gate driver B each have undervoltage lockout monitors. The device's logic input enters UVLO when VDDI  $\leq$  VDDI<sub>UV-</sub>, and exits UVLO when VDDI > VDDI<sub>UV+</sub>. The gate driver outputs, VOA and VOB, remain low when the logic input supply of the device is in UVLO, and their respective power supply (VDDA/B) is within the specified range. Each gate driver output can enter or exit UVLO independently. For example, VOA unconditionally enters UVLO when VDDA falls below VDDA<sub>UV-</sub> and exits UVLO when VDDA rises above VDDA<sub>UV+</sub>, while simultaneously VOB will behave as described in "4.1. Truth Tables" on page 9 if its related power supply, VDDB, is not in UVLO. See "4.2. Power Sequence and Timing Behavior" on page 11 and "4.1. Truth Tables" on page 9 for more details.

## 4.4. Logic Input Signals

#### 4.4.1. Control Inputs

VIA, VIB, PWM, EN, and DIS inputs are CMOS level-compatible, active-high inputs. When VDDI is in undervoltage lockout (UVLO), the inputs of these pins are ignored and the gate driver's outputs are pulled low. Disregarding the overlap protection behavior, for VIA/VIB input devices, the output follows the corresponding VIA or VIB input logic. For PWM input devices, VOA is high and VOB is low when the PWM input is high, and VOA is low and VOB is high when the PWM input is low. Please refer to "4.1. Truth Tables" on page 9 and "4.5. Dead Time Control and Overlap Protection" on page 13 for detailed information on overlap protection behavior.

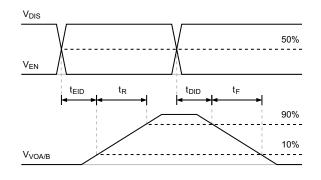

#### 4.4.2. Enable and Disable Input

For devices with an enable (EN) input, when the EN input is driven low, it unconditionally drives VOA and VOB low regardless of the states of VIA and VIB. Device operation terminates within  $t_{DID}$  after EN falls below  $V_{IL}$  and resumes within  $t_{EID}$  after EN rises above  $V_{IH}$ . For devices with a disable (DIS) input, when the DIS input is brought high, it unconditionally drives VOA and VOB low regardless of the states of VIA and VIB. Device operation terminates within  $t_{DID}$  after DIS rises above  $V_{IH}$  and resumes within  $t_{EID}$  after DIS falls below  $V_{IL}$ . See Figure 13, "Gate Driver Timing Behavior," on page 11 for more details. The EN and DIS inputs have no effect if VDDI is below its UVLO level (i.e., VOA, VOB remain low).

#### 4.4.3. Deglitch Filter

A deglitch feature is provided on some devices. The deglitch feature ignores input noise with a duration shorter than the deglitch filter setting, but also introduces additional propagation delay. See "6.2.4. Timing Characteristics" on page 33 for the delays associated with this feature. The deglitch filter can be adjusted by selecting different product options. See "10. Ordering Guide" on page 55 for more details.

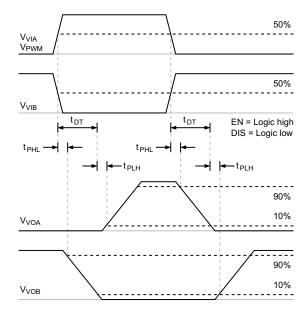

## 4.5. Dead Time Control and Overlap Protection

Dead time provides a user-programmable delay between the transitions of VOA and VOB. This delay is programmed by connecting a resistor ( $R_{DT}$ ) between the DT pin and ground. The appropriate value for  $R_{DT}$  can be determined from Equation 1 below.

$t_{DT} = 1.73 \times R_{DT} + 5.74$ Where:  $t_{DT}$  is the Typical Dead Time delay (ns)  $R_{DT}$  is the Dead Time Resistor (k $\Omega$ )

#### Equation 1.

The DT pin operates by outputting 0.9 V and monitoring the DT pin current.  $R_{DT}$  can be varied from 10 k $\Omega$  to 110 k $\Omega$ . With larger values of  $R_{DT}$ , the DT pin current can be very small and influenced by noise in the surrounding system. To aid in noise immunity, place a 0.1  $\mu$ F ceramic capacitor in parallel with  $R_{DT}$ . The capacitor should be placed as close to the DT pin as possible.

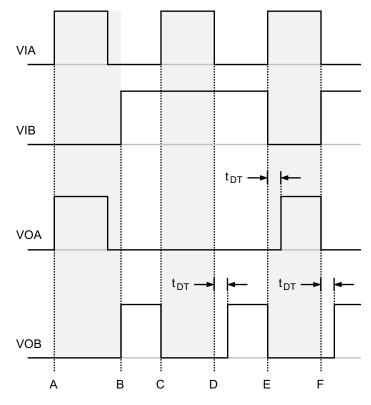

An input signal's falling edge activates the programmed dead time for the other signal. The output's dead time is always set to the longer of either the driver's programmed dead time or the input signal's own dead time. If both inputs are high simultaneously, both outputs will be immediately driven low. This overlap protection feature is used to prevent a shoot-through event and does not affect the programmed dead time setting for normal operation. Figure 14, "Dead Time and Overlap Protection Behavior," on page 14 illustrates and explains various driver dead time logic operating conditions.

Figure 14. Dead Time and Overlap Protection Behavior

For signal conditions designated A through F in the figure, note the following:

- A. The output VOA follows the input VIA exactly because VIB is already low.

- B. The output VOB follows the input VIB exactly because VIA is already low.

- C. The VIA input transitions high while the VIB input is already high. This causes both outputs, VOA and VOB, to immediately transition low due to overlap protection.

- D. The VIA input transitions low and assigns the programmed dead time to VOB. Output VOB is allowed to transition high after the programmed dead time.

- E. The VIA input transitions high simultaneously with the VIB input transitioning low. Output VOB immediately transitions low and assigns the programmed dead time to output VOA. The output VOA is allowed to transition high after the programmed dead time.

- F. The VIB input transitions high simultaneously with the VIA input transitioning low. Output VOA immediately transitions low and assigns the programmed dead time to output VOB. The output VOB is allowed to transition high after the programmed dead time.

For devices in the Universal configuration, both dead time and overlap protection can be disabled by connecting the DT input pin to VDDI, forcing the device to operate as a dual driver instead of a High-Side/Low-Side driver. The output VOA tracks the VIA input and output VOB tracks the VIB input without any intervening protection mechanisms.

Refer to "10. Ordering Guide" on page 55 for details on which specific OPNs provide dead time and overlap protection.

## 4.6. Selectable Variable Current Drive (SelVCD<sup>™</sup>)

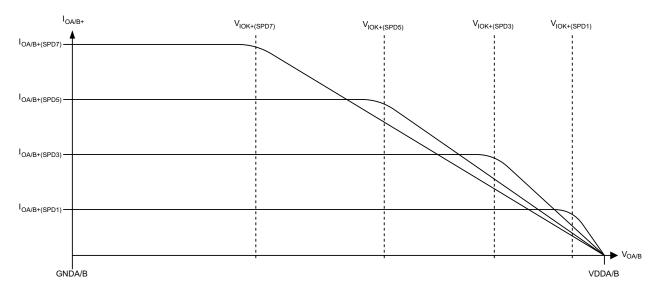

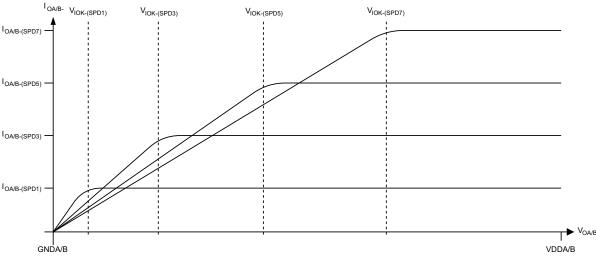

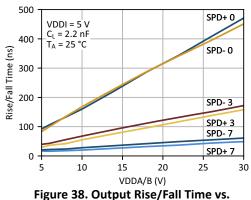

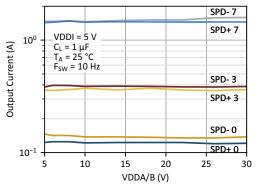

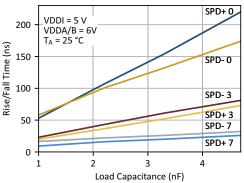

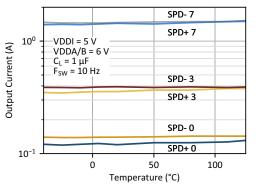

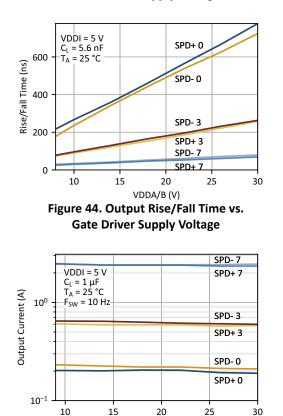

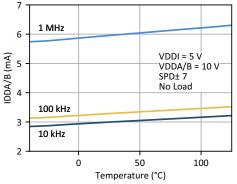

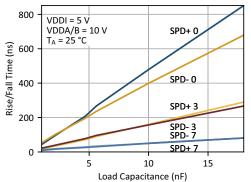

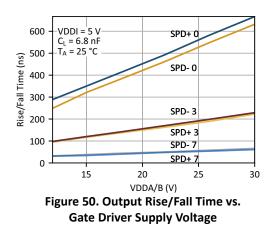

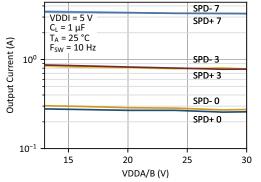

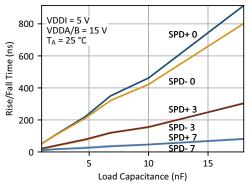

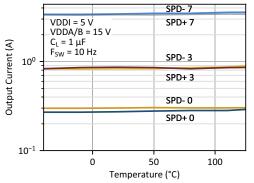

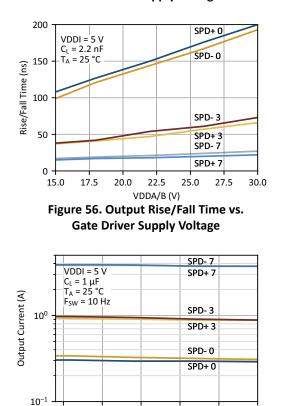

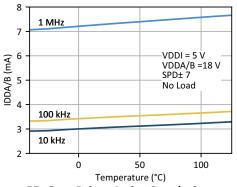

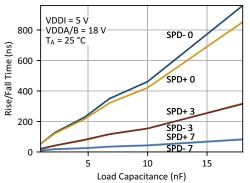

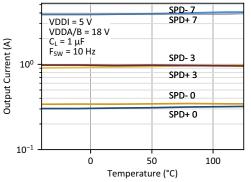

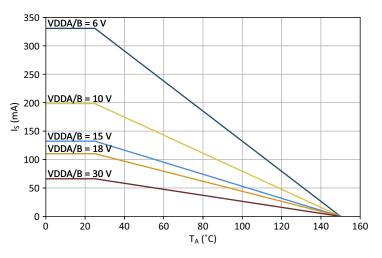

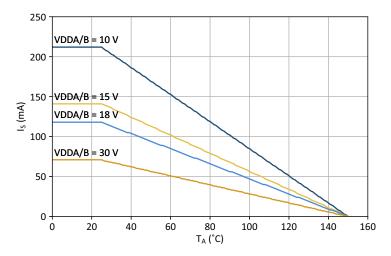

The gate driver output of the device operates as a current source, maintaining the driver's output current within ±10% of the typical value over temperature and semiconductor process variation for devices with an undervoltage lockout (UVLO) level of 8 V, 12 V and 15 V. The UVLO 4 V devices maintain their output current within ±15% of the typical value over temperature and semiconductor process variation as well. As the gate driver output behaves as a current source, the output current remains well-regulated over the gate driver supply voltage range. The typical output current is dependent on the gate driver UVLO level as defined in the "10. Ordering Guide" on page 55. The driver output will operate as a current source until it runs out of voltage headroom. In other words, the MOSFETs which comprise the gate drive output transition from the saturated region into the linear operating region. Typical headroom knees for SPD± 7, 5, 3, and 1 are shown in Figure 15, "SPD+ Output Current vs. Output Voltage," and Figure 16, "SPD– Output Current vs. Output Voltage," below. Note that SPD± settings not shown do exhibit the same behavior. See "6.2.3. Gate Driver Characteristics" on page 29 for details.

Figure 15. SPD+ Output Current vs. Output Voltage

Figure 16. SPD- Output Current vs. Output Voltage

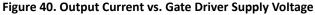

Each driver's output current, both sourcing and sinking, are user selectable among eight output current settings. The SPD+ pin controls the sourcing (turn-on) current and the SPD- pin controls the sinking (turn-off) current. Both outputs (VOA and VOB) are set to the same sourcing and sinking current setting indicated by the SPD± pins.

For static control of the SPD± pins, use 1% resistors between each SPD pin and ground. See "5.1. Recommended Application Circuits" on page 19 and the "SelVCD™ Resistor Settings" section of Table 6, "Logic Input Characteristics," on page 28 for more details. The SPD± pins operate by continuously sourcing I<sub>SPD±</sub> out of the pin and measuring the voltage at the pin.

If dynamic speed control is utilized, the resistors can be removed and a voltage source can be placed on the SPD± pins. For any specific speed (SPD) setting, ensure that the voltage on the SPD± pin is within the minimum and maximum bounds for the associated SPD level. See the "SelVCD<sup>M</sup> Voltage Settings" section of Table 6, "Logic Input Characteristics," on page 28 for information on SPD voltage bounds. Note that the voltage source must be able to sink I<sub>SPD±</sub> per SPD± pin.

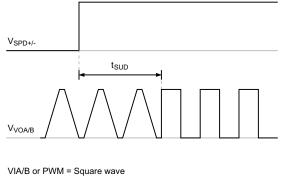

The sourcing and sinking current of VOA/B will change after Speed Update Delay (t<sub>SUD</sub>). See "AN1390: Methods for Dynamic Speed Control of the Si82Fx Performance Driver" for more details on implementing dynamic speed control.

SelVCD<sup>™</sup> eliminates the need for gate resistors and adds an integrated Miller clamp that operates through the gate driver output pin (VOA/B). The Miller clamp engages during the transition from V<sub>OH</sub> to V<sub>OL</sub>. When the output voltage, V<sub>OA/B</sub>, falls below V<sub>MCTA/B</sub>, the output speed setting temporarily changes from the current speed setting to SPD7– to maximize the sinking current. An example of the Miller clamp engaging is shown in Figure 17, "Miller Clamp Engagement Behavior," below. Note that if the current speed setting is SPD7–, no change will occur. The Miller clamp will stay engaged until the next V<sub>OL</sub> to V<sub>OH</sub> transition. If any voltage transients occur on VOA/B during the Off period, the Miller clamp will strongly clamp these to GNDA/B. The user-selected SPD– setting will be restored at the next V<sub>OL</sub> to V<sub>OL</sub> transition.

Figure 17. Miller Clamp Engagement Behavior

To achieve maximum Miller clamp performance, do not add any form of gate resistance between the gate driver output (VOA/B) and the power switch's gate or base. Usage of gate resistors will cause a voltage drop across the resistor, which will slow down turn-on and turn-off transitions and reduce the effectiveness of the Miller clamp.

In a traditional voltage-mode gate driver, external gate resistors dissipate a portion of the overall power required to charge and discharge the external power switch. As this power is dissipated internally in the Si82Fx, thermal protection (see "4.8. Thermal Protection" on page 17) will engage if power dissipation becomes excessive. See "5.3. Power Dissipation Considerations" on page 24 for more details.

# 4.7. Short-Circuit Clamp

The short circuit clamp is used to clamp voltages at the driver output (VOA/B) to slightly higher than the VDDA/B voltage during short circuit conditions. The short circuit clamp helps protect the driven switch gate from overvoltage breakdown or degradation. The clamp is implemented by adding a diode connection between VOA/B and the VDDA/B pins inside the driver. See "6.2.3. Gate Driver Characteristics" on page 29 for detailed specifications of this clamping feature. External diodes between VOA/B and VDDA/B can increase current conduction capability as needed.

## 4.8. Thermal Protection

The device includes a temperature sensor in each gate driver. Each sensor is monitored continuously. If the temperature exceeds the Trigger Temperature ( $T_{SD+}$ ), a thermal shutdown fault will occur, and the driver will pull low. After 1 ms, if the driver temperature fails to fall below the Reset Temperature ( $T_{SD-}$ ), the driver will pull weakly low. The driver will continuously pull weakly low until the temperature falls below  $T_{SD-}$ . Once the fault is removed, normal operation resumes.

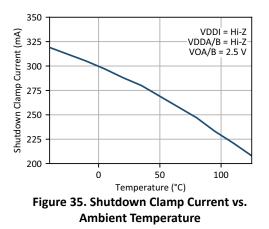

## 4.9. Shutdown Clamp

The device includes a voltage clamp between the gate driver output (VOA/B) and ground (GNDA/B) when the gate driver is unpowered (VDDA/B = high-Z). This clamp is sometimes referred to as an "active pull-down clamp". It provides a path to ground for transient currents which could otherwise cause parasitic turn-on of a driven switch when the gate driver is unpowered. See "6.2.3. Gate Driver Characteristics" on page 29 and "4.1. Truth Tables" on page 9 for details.

#### 4.10. ESD Structure

The Si82Fx device's I/O pin electrostatic discharge (ESD) diodes and associated supply pin ESD clamp diodes are illustrated in Figure 18, "Device ESD Structure," below. On the logic input side, a pair of ESD protection diodes are used on each input pin, and all upper diodes are connected to one shared clamp diode. This structure prevents the VDDI pin from being powered up through the input pin when the VDDI power supply is lost. The other clamp diode is present between the VDDI and GNDI pins. The ESD structure of the gate driver output is similar to the logic input, except that the upper diode is connected to a clamp diode at the VDDA/B pins.

Figure 18. Device ESD Structure

# 5. Application Information

The Si82Fx is designed to be both flexible and robust to meet a wide range of application requirements, safely survive overloads, and rapidly recover normal operation. To achieve these objectives, the appropriate Si82Fx device must be selected and its circuit carefully designed.

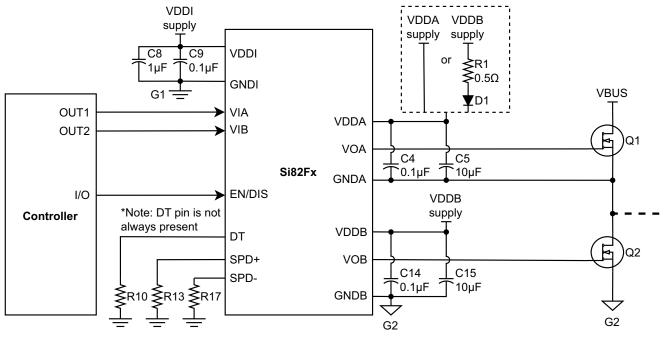

#### 5.1. Recommended Application Circuits

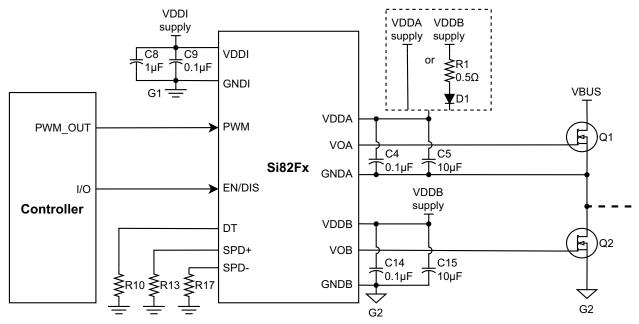

Figure 19, "High-Side/Low-Side Configuration," on page 20 illustrates a typical application circuit for a dual-input Si82Fx device connected in a half-bridge topology. Driver A of the Si82Fx device controls the high-side FET (Q1), and driver B controls the low-side FET (Q2). The controller provides the Si82Fx input signals (VIA and VIB) to control driver A and driver B. The Si82Fx device's input overlap protection feature ensures no concurrent conduction of FETs Q1 and Q2, even if both VIA and VIB input signals are High. The dead time is inserted before the rising edge of the gate drive signals. Since Q1 and Q2 FETs don't turn on or turn off instantly, the inserted dead time guarantees the opposite FET is completely off before the Si82Fx device turns on FETs Q1 or Q2. The dead time is adjustable through the R10 resistor connected to the DT pin. The controller can also use the EN/DIS signal to turn off both drivers immediately once a system fault is detected.

On the gate driver side, the Si82Fx device's SelVCD<sup>™</sup> feature eliminates the need for external high power rated gate resistors at the gate driver's output. Resistors R13 and R17 connected to the SPD+/- pins are used to control the gate driver's output current strength, as described in "4.6. Selectable Variable Current Drive (SelVCD™)" on page 15. Their values should be selected to meet the gate voltage rise-time/fall-time requirement based on the actual capacitive loading of FETs Q1 and Q2. G2 is the reference point or the reference ground of the gate drive output circuit. Figure 19, "High-Side/Low-Side Configuration," on page 20 also shows two possible power supply connections for the high-side gate driver A. VDDA can be powered by an isolated supply or powered by the same supply for Gate Driver B through the bootstrap circuit (resistor R1 and diode D1). The bootstrap circuit is the convenient way to power the high-side gate driver for the High-Side/Low-Side circuit configuration. Its basic operation follows. When FET Q2 is turned on, capacitors C4 and C5 are charged by the low-side VDDB supply through diode D1 and the conducting FET Q2. After FET Q2 is off, when FET Q1 is turned on, the reference potential of capacitors C4 and C5 jumps to VBUS, and thus diode D1 is reverse biased. In this situation, capacitors C4 and C5 act as the voltage source supplying current to gate driver A in order to maintain a logic high output. Resistor R1 is used to limit the inrush current of capacitors C4 and C5. Resistor R1 additionally limits the voltage slew rate between gate driver A's supply pins (VDDA and GNDA). More details about the bootstrap circuit can be found in "AN486: High-Side Bootstrap Design Using ISODrivers in Power Delivery Systems".

Two high-voltage Y2-class capacitors (not shown in the diagram) between the logic input reference (GNDI) and the two gate driver references (GNDA and GNDB) are recommended if additional radiated emissions or electrostatic discharge (ESD) mitigation is desired. The typical value for these two Y2 capacitors is between 47 pF and 100 pF. See "AN1131: Design Guide for Reducing Radiated and Conducted Emissions in Isolated Systems Using Skyworks' Isolators" for additional techniques to mitigate radiated and conducted emissions. Note that the Si82Fx device provides excellent common-mode transient immunity (CMTI) without employing any additional components or techniques. However, if your application requires extremely high common mode transient immunity (CMTI) performance, it is recommended to add a 10 nF capacitor between each of the logic input pins and the logic input ground (GNDI), including the no connect (NC) pins. This will help improve the CMTI performance.

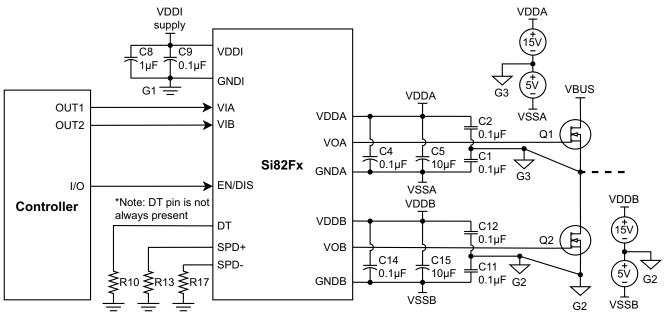

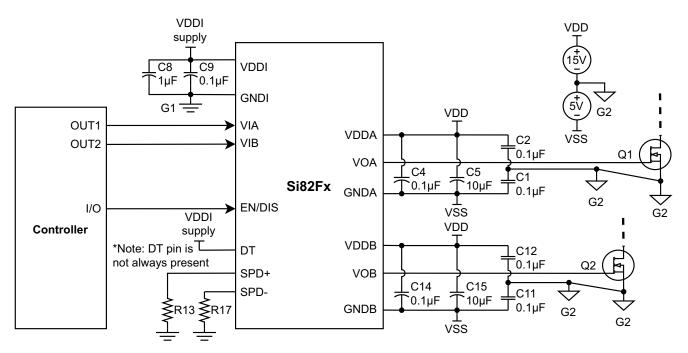

The diagram shown in Figure 20, "Bipolar Output Connection," on page 21 is similar to the above high-side/lowside configuration except that the drivers produce bipolar  $V_{GS}$  output voltage. The bipolar  $V_{GS}$  output requires the system to provide positive and negative voltage sources. Please note that the bootstrap circuit cannot be used to share the low-side voltage sources with the high-side Gate Driver A for a bipolar  $V_{GS}$  output application. In this example, +15 V and -5 V sources are used for low-side Gate Driver B, and its reference point is also G2. The other set of +15 V and -5 V sources are used for the high-side Gate Driver A. The high-side voltage sources' reference, G3, is electrically connected to FET Q1's source. Please note that the voltage potential at FET Q1's source jumps between VBUS and reference G2. Thus, the high-side voltage sources need to be isolated from reference G2 as well.

For the bipolar V<sub>GS</sub> output application, the additional bypass capacitors form a capacitor divider which serves to shorten the current flow loop. These capacitors should be placed close to the Si82Fx device's output power pins (VDDA/B). Taking the high-side gate driver A as an example, the ac component of the gate drive current flows from the VDDA net to the Si82Fx device's VDDA pin, VOA pin, Q1's gate, Q1's source, the midpoint of capacitors C1 and C2, and back to VDDA. Since the original bypass capacitors, C4 and C5, do not connect to reference G3 (which is connected to FET Q1's source), without capacitor C2, the return current needs to travel further to the system's +15 V source to complete the loop. This prolonged loop increases the chance of radiated emissions. Capacitors C11 and C12 serve the same purpose for the low-side FET Q2's gate drive return current.

Figure 20. Bipolar Output Connection

Figure 21, "PWM Input Application Circuit," below depicts an Si82Fx device with a high-side/low-side configuration and a PWM input.

This application circuit is similar to Figure 19, "High-Side/Low-Side Configuration," on page 20, except that the controller only provides the PWM input signal. The Si82Fx device will split the input signal phase, insert dead time, and drive the high-side and low-side FETs accordingly.

Figure 21. PWM Input Application Circuit

Figure 22, "Dual Low-Side Driver Application Circuit," below depicts the circuit for driving dual low-side FETs. When the dead time pin (DT) is tied to the logic input supply (VDDI), the Si82Fx device operates as a dual gate driver without overlap protection or dead time insertion. In this dual driver mode, the Si82Fx device can be used for high-side/low-side, dual high-side, dual low-side, or any circuit topology. However, the controller is responsible for providing overlap protection and dead-time insertion. In the dual low-side circuit topology depicted below, the +15 V and -5 V sources are shared by Gate Drivers A and B to generate bipolar V<sub>GS</sub> outputs. For a dual high-side application, Driver A and Driver B cannot share the same power supply and will require the individual isolated power supplies, even if the V<sub>GS</sub> output is unipolar.

Figure 22. Dual Low-Side Driver Application Circuit

# 5.2. Layout Considerations

The layout considerations are divided into general considerations for the entire device, the logic input side of the device, and the gate driver side. Please refer to "5.1. Recommended Application Circuits" on page 19 for specific parts referenced.

#### 5.2.1. General Considerations

- The bypass capacitors (usually 0.1  $\mu$ F || 10  $\mu$ F) should be placed close to the device's power supply pins and connected to the device with thick and short traces.

- The isolation barrier should have the required distance for the traces, power planes, ground planes, and copper areas on the device's logic input and gate drive sides.

- Safety isolation between gate drivers A and B on the gate driver side is usually not required. If the system needs safety isolation between gate drivers A and B, the trace, power plane, ground plane, and the copper area between the two gate drivers should have the required distance. Even though safety isolation between gate drivers A and B is usually not required, to avoid arcing through the air, the traces operating at high voltage should have some distance (approximately 1 mm per 1 kV) from the low voltage signals.

- The Si82Fx device is often used in high-power systems with significant switching current and transient voltage. Attention should be paid to the proximity and orientation of the Si82Fx device and any high-current switching circuits. This should also apply to the traces and components surrounding the Si82Fx device to avoid unwanted noise coupling.

#### 5.2.2. Logic Input Considerations

- Place resistors R10, R13, and R17 close to the Si82Fx device's dead time (DT) and speed (SPD±) pins, respectively.

- If your application requires extremely high common mode transient immunity (CMTI) performance, it is recommended to add a 10 nF capacitor between each of the logic input pins and the logic input ground (GNDI), including the no connect (NC) pins. This will help improve the CMTI performance.

- Using ≥6 mil trace width on all logic input pins is recommended. The interconnection between the controller and the Si82Fx device should be kept from any noisy signals in the system.

#### 5.2.3. Gate Driver Considerations

- If the system is designed to provide a bipolar V<sub>GS</sub> output, additional bypass capacitors (C1, C2, C11, and C12 in Figure 20, "Bipolar Output Connection," on page 21) are required to minimize the return path of the gate drive signals.

- It is recommended to use ≥20 mil trace width for the VOA/B gate driver traces and their return path.

- For a unipolar V<sub>GS</sub> output, the return path of the V<sub>GS</sub> gate drive signal is from the power device's source/ collector to the Si82Fx device's gate driver ground pin (GNDA/B). Explicitly use ≥20 mil trace width for this return current path and route this trace close to the VOA/B gate driver traces to reduce the loop area of the whole V<sub>GS</sub> gate drive signal. Moreover, it is a good practice to set the copper keep-out region along the return path trace so the system ground copper will not flood over this return trace.

- For a bipolar V<sub>GS</sub> output, the return path of the V<sub>GS</sub> gate drive signal is from the power device's source/ collector to the midpoint of capacitors C1/C2 or C11/C12. Therefore, these capacitors must be placed close to the Si82Fx device to minimize this current loop. Explicitly use ≥20 mil trace width for the return current path and route this return trace close to the VOA/VOB gate driver traces to reduce the loop area of the whole V<sub>GS</sub> gate drive signal. Moreover, it is a good practice to set the copper keep-out region along the return path trace so the system ground copper will not flood over this return trace.

- For a multiple-layer PCB design, ground and power planes are recommended to create a power supply current path with the least inductance. If there is no dedicated power or ground plane on the gate driver side, please use ≥20 mil trace width for the power supply connections.

- If the design utilizes Y2 capacitors between the logic input and gate drivers, the Y2 capacitors across the isolation barrier should be placed as close as possible to the sides of the Si82Fx device without pins.

# 5.3. Power Dissipation Considerations

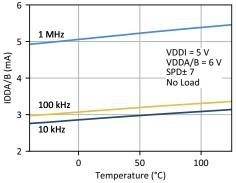

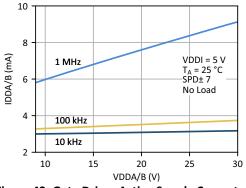

The device's average power dissipation is often required in order to estimate the silicon junction temperature. Since the Si82Fx doesn't utilize external gate resistors, the measured power consumption of the device is equal to its power dissipation. This is because the power switch being driven is a pure capacitive load, which doesn't consume real power. The device's power consumption is obtained by measuring the current consumption on each power supply input (VDDI, VDDA, and VDDB) and then multiplying it by its corresponding voltage.

Alternatively, the power dissipation can be estimated using the equation provided in "AN1339: Driver Power Dissipation Considerations". To solve the equation, the intended supply voltages, the load characteristics, and the switching frequency need to be collected. Skyworks provides a Microsoft Excel based calculator as part of "AN1339" to easily estimate the device's power dissipation and its silicon junction temperature.

# 6. Specifications

# 6.1. Absolute Maximum Ratings

| Parameter                  | Symbol                                    | Condition                         | Min   | Мах                                      | Unit |

|----------------------------|-------------------------------------------|-----------------------------------|-------|------------------------------------------|------|

| Storage Temperature        | T <sub>STG</sub>                          |                                   | -65   | 150                                      | °C   |

| Operating Temperature      | T <sub>A</sub>                            |                                   | -40   | 125                                      | °C   |

| Junction Temperature       | Tj                                        |                                   | _     | 150                                      | °C   |

| Logic Input Supply Voltage | VDDI                                      |                                   | -0.30 | 24                                       | V    |

| Gate Driver Supply Voltage | VDDA, VDDB                                |                                   | -0.30 | 36                                       | V    |

|                            | VIA, VIB, PWM, DT,<br>SPD+, SPD-, EN, DIS |                                   | -0.30 | VDDI + 0.3                               | V    |

| Input Signal Voltage       | VIA, VIB, PWM, SPD+,<br>SPD-, EN, DIS     | Transient for 100 ns <sup>2</sup> | -5.00 | VDDI + 0.3                               | V    |

| Output Signal Voltage      | VOA, VOB                                  |                                   | -0.30 | V <sub>DDA/B</sub> + V <sub>SCCA/B</sub> | V    |

|                            | VOA, VOB                                  | Transient for 200 ns <sup>2</sup> | -2.00 | V <sub>DDA/B</sub> + V <sub>SCCA/B</sub> | V    |

| Lead Solder Temperature    |                                           | Duration = 10 s                   | _     | 260                                      | °C   |

| ESD per AEC-Q100           |                                           |                                   |       |                                          |      |

| Human Body Model           | НВМ                                       |                                   | -4    | 4                                        | kV   |

| Charged Device Model       | CDM                                       |                                   | -2    | 2                                        | kV   |

#### Table 4. Absolute Maximum Ratings<sup>1</sup>

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. This parameter is not subject to production test. It is guaranteed by characterization.

ESD Handling: Industry-standard ESD handling precautions must be adhered to at all times to avoid damage to this device.

# **6.2. Electrical Characteristics**

The following tables provide electrical parametric data for this device.

#### 6.2.1. Power Supply Characteristics

#### Table 5. Power Supply Characteristics<sup>1</sup>

Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V;  $T_A = -40$  to +125 °C;  $F_{IN} \le 1$  MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                      | Symbol                                | Test Condition                                        | Min  | Тур  | Max  | Unit |

|--------------------------------|---------------------------------------|-------------------------------------------------------|------|------|------|------|

| Supply Voltage                 |                                       | I                                                     |      |      |      |      |

| Logic Input Supply             | VDDI                                  |                                                       | 3.00 | -    | 20.0 | V    |

| Gate Driver Supply             | VDDA, VDDB                            |                                                       | 5.00 | -    | 30.0 | V    |

| Supply Current                 |                                       |                                                       |      |      |      |      |

| Logic Input Supply             |                                       |                                                       |      |      |      |      |

| Quiescent Current              | IDDI <sub>Q</sub>                     | EN = logic low or<br>DIS = logic high                 | _    | 1.57 | 1.82 | mA   |

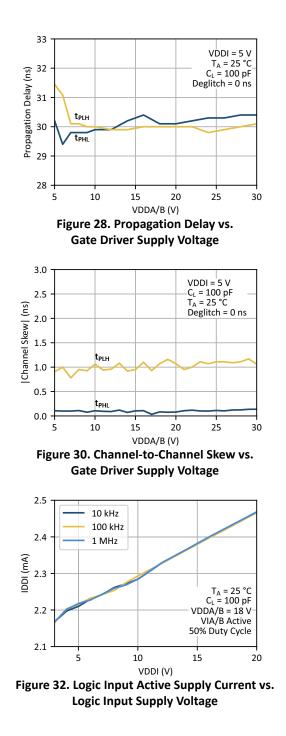

| Active Current                 | IDDI                                  | VIA/B = 1 MHz;<br>50% duty cycle                      | _    | 2.45 | 2.74 | mA   |

| Gate Driver Supply             |                                       |                                                       |      |      |      |      |

| 4 V Undervoltage Lockout (Si82 | FxxxGx) Devices                       |                                                       |      |      |      |      |

| Quiescent Current              | IDDA <sub>Q</sub> , IDDB <sub>Q</sub> | EN = logic low or<br>DIS = logic high                 | _    | 2.93 | 4.02 | mA   |

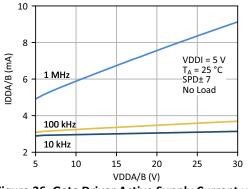

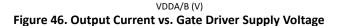

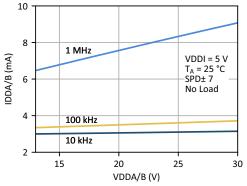

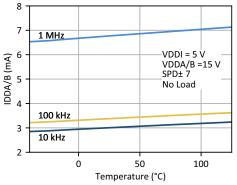

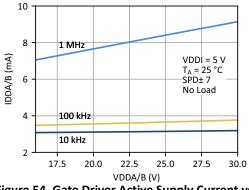

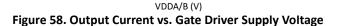

| Active Current                 | IDDA, IDDB                            | VOA/B = 1 MHz;<br>50% duty cycle; no load;<br>Speed 7 | _    | 5.99 | 13.2 | mA   |

| 8 V Undervoltage Lockout (Si82 | 2FxxxBx) Devices                      |                                                       |      |      |      |      |

| Quiescent Current              | IDDA <sub>Q</sub> , IDDB <sub>Q</sub> | EN = logic low or<br>DIS = logic high                 | _    | 2.95 | 4.02 | mA   |

| Active Current                 | IDDA, IDDB                            | VOA/B = 1 MHz;<br>50% duty cycle; no load;<br>Speed 7 | _    | 7.14 | 13.2 | mA   |

| 12 V Undervoltage Lockout (Si  | 82FxxxCx) Devices                     |                                                       |      |      |      |      |

| Quiescent Current              | IDDA <sub>Q</sub> , IDDB <sub>Q</sub> | EN = logic low or<br>DIS = logic high                 | _    | 3.00 | 4.02 | mA   |

| Active Current                 | IDDA, IDDB                            | VOA/B = 1 MHz;<br>50% duty cycle; no load;<br>Speed 7 | _    | 8.51 | 13.2 | mA   |

| 15 V Undervoltage Lockout (Si  | 32FxxxEx) Devices                     |                                                       |      | •    |      |      |

| Quiescent Current              | IDDA <sub>Q</sub> , IDDB <sub>Q</sub> | EN = logic low or<br>DIS = logic high                 | _    | 3.06 | 4.02 | mA   |

| Active Current                 | IDDA, IDDB                            | VOA/B = 1 MHz;<br>50% duty cycle; no load;<br>Speed 7 | _    | 9.33 | 13.2 | mA   |

| Undervoltage Lockout           | 1                                     | 1                                                     |      | I    | 1    | 1    |

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com 206821A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice

#### Table 5. Power Supply Characteristics<sup>1</sup> (Continued)

Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V;  $T_A = -40$  to +125 °C;  $F_{IN} \le 1$  MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                      | Symbol                                    | Test Condition | Min   | Тур   | Max   | Unit |

|--------------------------------|-------------------------------------------|----------------|-------|-------|-------|------|

| Logic Input Supply             |                                           |                |       |       |       |      |

| Positive-Going Threshold       | VDDI <sub>UV+</sub>                       | VDDI rising    | 2.76  | 2.88  | 2.99  | v    |

| Negative-Going Threshold       | VDDI <sub>UV-</sub>                       | VDDI falling   | 2.64  | 2.78  | 2.94  | v    |

| Threshold Hysteresis           | VDDI <sub>HYS</sub>                       |                | -     | 100   | -     | mV   |

| Gate Driver Supply             |                                           |                | I     | l     |       |      |

| 4 V Undervoltage Lockout (Si82 | FxxxGx) Devices                           |                |       |       |       |      |

| Positive-Going Threshold       | VDDA <sub>UV+</sub> , VDDB <sub>UV+</sub> | VDDA/B rising  | 4.09  | 4.30  | 4.54  | N    |

| Negative-Going Threshold       | VDDA <sub>UV</sub> , VDDB <sub>UV</sub>   | VDDA/B falling | 3.89  | 4.10  | 4.33  | V    |

| Threshold Hysteresis           | VDDA <sub>HYS</sub> , VDDB <sub>HYS</sub> |                | -     | 200   | -     | mV   |

| 8 V Undervoltage Lockout (Si82 | PxxxBx) Devices                           |                | I     | l     |       |      |

| Positive-Going Threshold       | VDDA <sub>UV+</sub> , VDDB <sub>UV+</sub> | VDDA/B rising  | 7.58  | 8.07  | 8.55  | N    |

| Negative-Going Threshold       | VDDA <sub>UV</sub> , VDDB <sub>UV</sub>   | VDDA/B falling | 7.14  | 7.57  | 8.05  | V    |

| Threshold Hysteresis           | VDDA <sub>HYS</sub> , VDDB <sub>HYS</sub> |                | _     | 500   | -     | mV   |

| 12 V Undervoltage Lockout (Si8 | 2FxxxCx) Devices                          |                | 1     | 1     |       |      |

| Positive-Going Threshold       | VDDA <sub>UV+</sub> , VDDB <sub>UV+</sub> | VDDA/B rising  | 11.21 | 11.90 | 12.61 |      |

| Negative-Going Threshold       | VDDA <sub>UV</sub> , VDDB <sub>UV</sub>   | VDDA/B falling | 10.29 | 10.90 | 11.52 | V    |

| Threshold Hysteresis           | VDDA <sub>HYS</sub> , VDDB <sub>HYS</sub> |                | -     | 1.00  | -     | V    |

| 15 V Undervoltage Lockout (Si8 | 2FxxxEx) Devices                          |                | 1     | 1     | 1     | 1    |

| Positive-Going Threshold       | VDDA <sub>UV+</sub> , VDDB <sub>UV+</sub> | VDDA/B rising  | 14.19 | 15.15 | 16.13 | N.   |

| Negative-Going Threshold       | VDDA <sub>UV</sub> , VDDB <sub>UV</sub>   | VDDA/B falling | 13.81 | 14.70 | 15.66 | V    |

| Threshold Hysteresis           | VDDA <sub>HYS</sub> , VDDB <sub>HYS</sub> |                | _     | 450   | _     | mV   |

1. Adding the suffix A/B to any symbol, parameter, or test condition variable denotes that the term applies interchangeably to either Gate Driver A or Gate Driver B.

### 6.2.2. Logic Input Characteristics

#### **Table 6. Logic Input Characteristics**

Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V;  $T_A = -40$  to +125 °C;  $F_{IN} \le 1$  MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                                          | Symbol                                  | Test Condition                    | Min         | Тур         | Max         | Unit |

|----------------------------------------------------|-----------------------------------------|-----------------------------------|-------------|-------------|-------------|------|

| Input Threshold                                    |                                         |                                   |             |             |             |      |

| High Input                                         | V <sub>IH</sub>                         | VIA, VIB, PWM,<br>EN, DIS rising  | VDDI x 0.75 | _           | -           | V    |

| Low Input                                          | V <sub>IL</sub>                         | VIA, VIB, PWM,<br>EN, DIS falling | _           | _           | VDDI x 0.25 | V    |

| Hysteresis                                         | V <sub>HYS</sub>                        | VIA, VIB, PWM,<br>EN, DIS         | VDDI x 0.10 | VDDI x 0.15 | _           | V    |

| Input Pull-Down Resistance                         | R <sub>I</sub>                          | VIA, VIB, PWM,<br>EN, DIS         | 125         | 200         | 320         | kΩ   |

| Input Leakage Current                              | I <sub>LKG</sub>                        | VIA, VIB, PWM,<br>EN, DIS         | _           | _           | 140         | μΑ   |

| SelVCD <sup>™</sup> Resistor Settings <sup>1</sup> |                                         | 1                                 |             | 1           |             |      |

| Speed 0                                            | R <sub>SPD0+</sub> , R <sub>SPD0-</sub> | SPD+, SPD-                        | -           | 0.00        | —           | kΩ   |

| Speed 1                                            | R <sub>SPD1+</sub> , R <sub>SPD1-</sub> | SPD+, SPD-                        | -           | 2.67        | _           | kΩ   |

| Speed 2                                            | R <sub>SPD2+</sub> , R <sub>SPD2-</sub> | SPD+, SPD-                        | -           | 4.12        | _           | kΩ   |

| Speed 3                                            | R <sub>SPD3+</sub> , R <sub>SPD3-</sub> | SPD+, SPD-                        | -           | 5.62        | —           | kΩ   |

| Speed 4                                            | R <sub>SPD4+</sub> , R <sub>SPD4-</sub> | SPD+, SPD-                        | -           | 7.32        | _           | kΩ   |

| Speed 5                                            | R <sub>SPD5+</sub> , R <sub>SPD5-</sub> | SPD+, SPD-                        | -           | 9.53        | _           | kΩ   |

| Speed 6                                            | R <sub>SPD6+</sub> , R <sub>SPD6-</sub> | SPD+, SPD-                        | -           | 12.4        | —           | kΩ   |

| Speed 7 <sup>2</sup>                               | R <sub>SPD7+</sub> , R <sub>SPD7-</sub> | SPD+, SPD-                        | -           | 15.8        | —           | kΩ   |

| SelVCD <sup>™</sup> Voltage Settings               |                                         |                                   |             | l           |             |      |

| Speed 0                                            | V <sub>SPD0+</sub> , V <sub>SPD0-</sub> | SPD+, SPD-                        | 0.00        | -           | 85.0        | mV   |

| Speed 1                                            | V <sub>SPD1+</sub> , V <sub>SPD1-</sub> | SPD+, SPD-                        | 127         | -           | 145         | mV   |

| Speed 2                                            | V <sub>SPD2+</sub> , V <sub>SPD2-</sub> | SPD+, SPD-                        | 197         | _           | 224         | mV   |

| Speed 3                                            | V <sub>SPD3+</sub> , V <sub>SPD3-</sub> | SPD+, SPD-                        | 268         | _           | 306         | mV   |

| Speed 4                                            | V <sub>SPD4+</sub> , V <sub>SPD4-</sub> | SPD+, SPD-                        | 350         | _           | 398         | mV   |

| Speed 5                                            | V <sub>SPD5+</sub> , V <sub>SPD5-</sub> | SPD+, SPD-                        | 455         | -           | 518         | mV   |

| Speed 6                                            | V <sub>SPD6+</sub> , V <sub>SPD6-</sub> | SPD+, SPD-                        | 593         | _           | 674         | mV   |

| Speed 7 <sup>2</sup>                               | V <sub>SPD7+</sub> , V <sub>SPD7-</sub> | SPD+, SPD-                        | 755         | _           | 858         | mV   |

| SelVCD™ Resistor Current                           | I <sub>SPD+</sub> , I <sub>SPD-</sub>   | SPD+, SPD-                        | 49.3        | 51.0        | 52.7        | μA   |

1. Specified with E96 1% accuracy resistors. See "4.6. Selectable Variable Current Drive (SelVCD™)" on page 15 for more information.

2. The SPD+ or SPD- pins may also be tied to VDDI to select Speed 7.

## 6.2.3. Gate Driver Characteristics

#### Table 7. Gate Driver Characteristics<sup>1</sup>

Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V;  $T_A = -40$  to +125 °C;  $F_{IN} = 1$  MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                        | Symbol                                   | Test Condition                                      | Min              | Тур  | Max  | Unit |

|----------------------------------|------------------------------------------|-----------------------------------------------------|------------------|------|------|------|

| Output Voltage                   |                                          |                                                     |                  |      |      |      |

| Logic High (Sourcing)            | V <sub>OHA</sub> , V <sub>OHB</sub>      | I <sub>OA/B</sub> = -20 mA                          | VDDA/B x<br>0.98 | _    | _    | v    |

| Logic Low (Sinking)              | V <sub>OLA</sub> , V <sub>OLB</sub>      | I <sub>OA/B</sub> = 20 mA                           | —                | _    | 0.10 | V    |

| Output Resistance                |                                          | -                                                   |                  |      |      |      |

| Logic High (Sourcing)            | R <sub>ONA+</sub> , R <sub>ONB+</sub>    | 15 V UVLO, SPD 7                                    | —                | 1.00 | -    | Ω    |

| Logic Low (Sinking)              | R <sub>ONA</sub> , R <sub>ONB</sub>      |                                                     | —                | 0.70 | -    | Ω    |

| Output Current                   | ·                                        |                                                     |                  |      | -    |      |

| 4 V Undervoltage Lockout (Si82Fx | xxGx) Devices                            |                                                     |                  |      |      |      |

| Logic High (Sourcing)            | I <sub>OA+</sub> , I <sub>OB+</sub>      | Speed 7, VDDA/B = 6 V,<br>$V_{OA/B}$ = 1.5 V        | 1.27             | 1.50 | 1.73 | А    |

| Logic Low (Sinking)              | I <sub>OA</sub> , I <sub>OB</sub>        | Speed 7, VDDA/B = 6 V,<br>$V_{OA/B}$ = 4.5 V        | 1.27             | 1.50 | 1.73 | А    |

| 8 V Undervoltage Lockout (Si82Fx | xxBx) Devices                            |                                                     |                  |      |      |      |

| Logic High (Sourcing)            | I <sub>OA+</sub> , I <sub>OB+</sub>      | Speed 7, VDDA/B = 10 V,<br>V <sub>OA/B</sub> = 3 V  | 2.25             | 2.50 | 2.75 | A    |

| Logic Low (Sinking)              | I <sub>OA</sub> ., I <sub>OB</sub> .     | Speed 7, VDDA/B = 10 V,<br>V <sub>OA/B</sub> = 7 V  | 2.25             | 2.50 | 2.75 | А    |

| 12 V Undervoltage Lockout (Si82F | xxxCx) Devices                           |                                                     |                  |      |      |      |

| Logic High (Sourcing)            | I <sub>OA+</sub> , I <sub>OB+</sub>      | Speed 7, VDDA/B = 15 V,<br>V <sub>OA/B</sub> = 5 V  | 3.15             | 3.50 | 3.85 | А    |

| Logic Low (Sinking)              | I <sub>OA</sub> , I <sub>OB</sub>        | Speed 7, VDDA/B = 15 V,<br>V <sub>OA/B</sub> = 10 V | 3.15             | 3.50 | 3.85 | A    |

| 15 V Undervoltage Lockout (Si82F | xxxEx) Devices                           |                                                     |                  |      | -    |      |

| Logic High (Sourcing)            | I <sub>OA+</sub> , I <sub>OB+</sub>      | Speed 7, VDDA/B = 18 V,<br>V <sub>OA/B</sub> = 6 V  | 3.60             | 4.00 | 4.40 | А    |

| Logic Low (Sinking)              | I <sub>OA</sub> , I <sub>OB</sub>        | Speed 7, VDDA/B = 18 V,<br>V <sub>OA/B</sub> = 12 V | 3.60             | 4.00 | 4.40 | А    |

| Dutput Current Ratio             | ·                                        |                                                     |                  |      |      |      |

| Logic High (Sourcing)            |                                          |                                                     |                  |      |      |      |

| Speed 0                          | $\Delta_{IOA+(0:7)}, \Delta_{IOB+(0:7)}$ | I <sub>OA/B(SPD0)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 5.08             | 8.75 | 12.6 | %    |

| Speed 1                          | $\Delta_{IOA+(1:7)}, \Delta_{IOB+(1:7)}$ | I <sub>OA/B(SPD1)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 8.93             | 12.5 | 16.9 | %    |

| Speed 2                          | $\Delta_{IOA+(2:7)}, \Delta_{IOB+(2:7)}$ | I <sub>OA/B(SPD2)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 14.1             | 17.5 | 23.3 | %    |

| Speed 3                          | $\Delta_{IOA+(3:7)}, \Delta_{IOB+(3:7)}$ | I <sub>OA/B(SPD3)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 20.1             | 25.0 | 31.7 | %    |

| Speed 4                          | $\Delta_{IOA+(4:7)}, \Delta_{IOB+(4:7)}$ | I <sub>OA/B(SPD4)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 30.9             | 35.0 | 42.8 | %    |

| Speed 5                          | $\Delta_{IOA+(5:7)}, \Delta_{IOB+(5:7)}$ | I <sub>OA/B(SPD5)</sub> ÷ I <sub>OA/B(SPD7)</sub>   | 44.6             | 50.0 | 58.6 | %    |

Skyworks Solutions, Inc. • Phone [949] 231-3000 • sales@skyworksinc.com • www.skyworksinc.com 206821A • Skyworks Proprietary Information • Products and Product Information are Subject to Change without Notice

Table 7. Gate Driver Characteristics<sup>1</sup> (Continued)Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V; T<sub>A</sub> = -40 to +125 °C; F<sub>IN</sub> = 1 MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                        | Symbol                                                 | Test Condition                                    | Min  | Тур                 | Max  | Unit     |

|----------------------------------|--------------------------------------------------------|---------------------------------------------------|------|---------------------|------|----------|

| Speed 6                          | $\Delta_{\text{IOA+(6:7)}}, \Delta_{\text{IOB+(6:7)}}$ | I <sub>OA/B(SPD6)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 62.9 | 70.0                | 79.2 | %        |

| Speed 7                          | Δ <sub>IOA+(7:7)</sub> , Δ <sub>IOB+(7:7)</sub>        | I <sub>OA/B(SPD7)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 100  | 100                 | 100  | %        |

| Logic Low (Sinking)              |                                                        |                                                   | L    |                     |      |          |

| Speed 0                          | Δ <sub>IOA-(0:7)</sub> , Δ <sub>IOB-(0:7)</sub>        | I <sub>OA/B(SPD0)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 5.67 | 8.75                | 14.5 | %        |

| Speed 1                          | Δ <sub>IOA-(1:7)</sub> , Δ <sub>IOB-(1:7)</sub>        | I <sub>OA/B(SPD1)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 9.89 | 12.5                | 18.4 | %        |

| Speed 2                          | Δ <sub>IOA-(2:7)</sub> , Δ <sub>IOB-(2:7)</sub>        | I <sub>OA/B(SPD2)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 15.6 | 17.5                | 24.4 | %        |

| Speed 3                          | Δ <sub>IOA-(3:7)</sub> , Δ <sub>IOB-(3:7)</sub>        | I <sub>OA/B(SPD3)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 22.9 | 25.0                | 32.4 | %        |

| Speed 4                          | Δ <sub>IOA-(4:7)</sub> , Δ <sub>IOB-(4:7)</sub>        | I <sub>OA/B(SPD4)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 33.0 | 35.0                | 45.6 | %        |

| Speed 5                          | Δ <sub>IOA-(5:7)</sub> , Δ <sub>IOB-(5:7)</sub>        | I <sub>OA/B(SPD5)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 45.7 | 50.0                | 61.0 | %        |

| Speed 6                          | Δ <sub>IOA-(6:7)</sub> , Δ <sub>IOB-(6:7)</sub>        | I <sub>OA/B(SPD6)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 65.9 | 70.0                | 81.5 | %        |

| Speed 7                          | Δ <sub>IOA-(7:7)</sub> , Δ <sub>IOB-(7:7)</sub>        | I <sub>OA/B(SPD7)</sub> ÷ I <sub>OA/B(SPD7)</sub> | 100  | 100                 | 100  | %        |

| Output Current Knee              |                                                        |                                                   | L    |                     |      |          |

| 4 V Undervoltage Lockout (Si82Fx | xxGx) Devices                                          |                                                   |      |                     |      |          |

| Logic High (Sourcing)            |                                                        |                                                   |      |                     |      |          |

| Speed 1                          | V <sub>IOK+(SPD1)</sub>                                |                                                   | _    | 4.05                | _    | V        |

| Speed 3                          | V <sub>IOK+(SPD3)</sub>                                |                                                   | _    | 3.90                | _    | V        |

| Speed 5                          | V <sub>IOK+(SPD5)</sub>                                | VDDA/B = 6 V                                      | _    | 3.60                | _    | V        |

| Speed 7                          | V <sub>IOK+(SPD7)</sub>                                |                                                   | _    | 3.10                | _    | V        |

| Logic Low (Sinking) <sup>2</sup> | ł                                                      |                                                   |      |                     |      |          |

| Speed 1                          | V <sub>IOK-(SPD1)</sub>                                |                                                   | —    | V <sub>MCTA/B</sub> | -    | V        |

| Speed 3                          | V <sub>IOK-(SPD3)</sub>                                |                                                   | _    | V <sub>MCTA/B</sub> | -    | V        |

| Speed 5                          | V <sub>IOK-(SPD5)</sub>                                | VDDA/B = 6 V                                      | _    | V <sub>MCTA/B</sub> | _    | V        |

| Speed 7                          | V <sub>IOK-(SPD7)</sub>                                |                                                   | _    | V <sub>MCTA/B</sub> | -    | V        |

| 8 V Undervoltage Lockout (Si82Fx | xxBx) Devices                                          |                                                   |      |                     |      |          |

| Logic High (Sourcing)            |                                                        |                                                   |      |                     |      |          |

| Speed 1                          | V <sub>IOK+(SPD1)</sub>                                |                                                   | _    | 6.75                | _    | V        |

| Speed 3                          | V <sub>IOK+(SPD3)</sub>                                |                                                   | _    | 6.45                | _    | V        |

| Speed 5                          | V <sub>IOK+(SPD5)</sub>                                | VDDA/B = 10 V                                     | _    | 6.10                | _    | V        |

| Speed 7                          | V <sub>IOK+(SPD7)</sub>                                | 1                                                 | _    | 5.45                | _    | V        |

| Logic Low (Sinking) <sup>2</sup> | 1                                                      |                                                   | 1    |                     | I    | <u>ı</u> |

| Speed 1                          | V <sub>IOK-(SPD1)</sub>                                |                                                   | _    | V <sub>MCTA/B</sub> | _    | V        |

| Speed 3                          | V <sub>IOK-(SPD3)</sub>                                |                                                   |      | V <sub>MCTA/B</sub> | _    | V        |

| Speed 5                          | V <sub>IOK</sub> -(SPD5)                               | VDDA/B = 10 V                                     | _    | V <sub>MCTA/B</sub> | _    | V        |

| Speed 7                          | V <sub>IOK-(SPD7)</sub>                                | 1                                                 | _    | 3.40                | _    | V        |

Table 7. Gate Driver Characteristics<sup>1</sup> (Continued)Operating range for the following specifications: VDDI = 3.0-20 V; VDDA/B = 5.0-30 V; T<sub>A</sub> = -40 to +125 °C; F<sub>IN</sub> = 1 MHz.

Typical specifications: VDDI = 5 V; VDDA/B = 6 V for 4 V UVLO devices, 10 V for 8 V UVLO devices, 15 V for 12 V UVLO devices, 18 V for 15 V UVLO devices;  $T_A = 25$  °C unless otherwise noted.

| Parameter                       | Symbol                  | Test Condition  | Min | Тур   | Max | Unit |

|---------------------------------|-------------------------|-----------------|-----|-------|-----|------|

| 12 V Undervoltage Lockout (Si82 | FxxxCx) Devices         |                 |     |       |     |      |

| Logic High (Sourcing)           |                         |                 |     |       |     |      |

| Speed 1                         | V <sub>IOK+(SPD1)</sub> |                 | -   | 9.90  | _   | V    |

| Speed 3                         | V <sub>IOK+(SPD3)</sub> | VDDA/B = 15 V   | _   | 9.65  | _   | V    |

| Speed 5                         | V <sub>IOK+(SPD5)</sub> | VDDAYB - 15 V   | _   | 9.20  | _   | V    |

| Speed 7                         | V <sub>IOK+(SPD7)</sub> |                 | _   | 8.40  | _   | V    |

| Logic Low (Sinking)             | •                       | •               | •   | •     | •   |      |

| Speed 1                         | V <sub>IOK-(SPD1)</sub> |                 | -   | 2.50  | —   | V    |

| Speed 3                         | V <sub>IOK-(SPD3)</sub> | VDDA/B = 15 V   | _   | 2.95  | —   | V    |

| Speed 5                         | V <sub>IOK-(SPD5)</sub> |                 | _   | 3.65  | —   | V    |