# 8-Bit, 50MSPS, Video A/D Converter with Clamp Function

The HI2302 is an 8-bit CMOS A/D Converter for video with synchronizing clamp function. The adoption of two-step parallel method achieves low power consumption and a maximum conversion rate of 50MSPS. For pin compatible lower sample rate converters refer to HI1179 (35MSPS) or HI1176 (20MSPS) data sheets.

### **Ordering Information**

| PART<br>NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG. NO.  |

|----------------|---------------------|------------|-----------|

| HI2302JCQ      | -40 to 85           | 32 Ld MQFP | Q32.7x7-S |

# **Applications**

- Video Digitizing

- · Wireless Receivers

- LCD Projectors/Panels

- · Cable Modems

- RGB Graphics Processing

- Camcorders

- Instrumentation

#### **Features**

| • | Resolution                                         | 8-Bit ±0.5 LSB (DNL) |

|---|----------------------------------------------------|----------------------|

| • | Maximum Sampling Frequency                         | 50 MSPS              |

| • | Low Power Consumption (Reference Current Excluded) |                      |

- Built-In Input Clamp Function (DC Restore)

- Clamp ON/OFF Function

- Internal Voltage Reference

- Input CMOS/TTL Compatible

- Three-State TTL Compatible Output

- Power Supply . . . . . . . . . . . . . . . . . . +5V Single or +5V/3.3V Dual

- Direct Replacement for Sony CXD2302Q

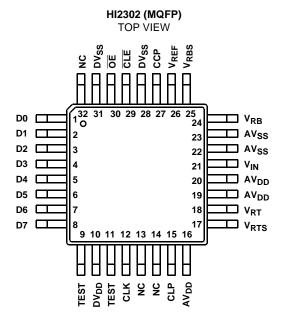

#### **Pinout**

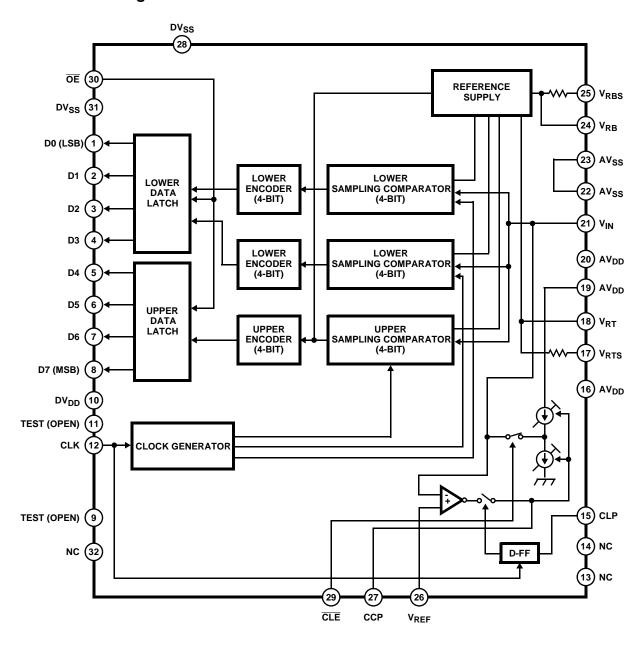

# Functional Block Diagram

### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

| Supply Voltage (V <sub>DD</sub> )                                                                   | V |

|-----------------------------------------------------------------------------------------------------|---|

| Reference Voltage (V <sub>RT</sub> , V <sub>RB</sub> ) V <sub>DD</sub> +0.5 to V <sub>SS</sub> -0.5 | V |

| Input Voltage (Analog) (V <sub>IN</sub> ) V <sub>DD</sub> +0.5 to V <sub>SS</sub> -0.5              | V |

| Input Voltage (Digital) (V <sub>I</sub> ) V <sub>DD</sub> +0.5 to V <sub>SS</sub> -0.5              | V |

| Output Voltage (Digital) (VO) VDD +0.5 to VSS -0.5                                                  | V |

#### **Operating Conditions**

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | $\theta_{JA}$ (°C/W)                   |

|------------------------------------------------|----------------------------------------|

| MQFP Package                                   | 122                                    |

| Maximum Junction Temperature (Plastic Package) | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range55            | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s)       |                                        |

| (MQFP - Lead Tips Only)                        |                                        |

|                                                |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

### $\textbf{Electrical Specifications} \quad \text{ f}_{\text{C}} = 50 \text{ MSPS, AV}_{\text{DD}} = 5 \text{V, DV}_{\text{DD}} = 3 \text{ to } 5.5 \text{V, V}_{\text{RB}} = 0.5 \text{V, V}_{\text{RT}} = 2.5 \text{V, T}_{\text{A}} = 25 ^{\text{O}} \text{C}$

| PARAMETER                       | SYMBOL             | TEST CO                                                                                                                     | NOTES                   | MIN    | TYP | MAX  | UNITS |         |

|---------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|-----|------|-------|---------|

| ANALOG CHARACTERISTICS          | 3                  | •                                                                                                                           |                         |        |     | '    | '     | "       |

| Maximum Conversion Rate         | f <sub>C</sub> Max | $AV_{DD} = 4.75 \text{ to } 5.25 \text{V},$                                                                                 |                         | 50     | 65  | -    | MSPS  |         |

| Minimum Conversion Rate         | f <sub>C</sub> Min | 0.5 to 2.5V,<br>f <sub>IN</sub> = 1kHz Triangular V                                                                         |                         | -      | -   | 0.5  | MSPS  |         |

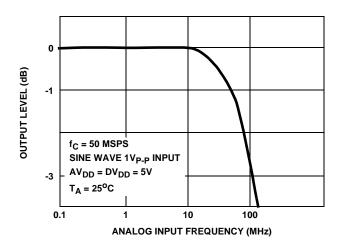

| Input Bandwidth Full Scale      | BW                 | Envelope                                                                                                                    | -1dB                    |        | -   | 60   | -     | MHz     |

|                                 |                    | $R_{IN} = 33\Omega$                                                                                                         | -3dB                    |        | -   | 100  | -     | MHz     |

| Differential Nonlinearity Error | E <sub>D</sub>     | End Point                                                                                                                   |                         |        | -   | ±0.3 | ±0.5  | LSB     |

| Integral Nonlinearity Error     | EL                 |                                                                                                                             |                         |        | -   | +0.7 | ±1.5  | LSB     |

| Offset Voltage                  | E <sub>OT</sub>    | Potential Difference to \                                                                                                   | / <sub>RT</sub>         | Note 2 | -70 | -50  | -30   | mV      |

|                                 | E <sub>OB</sub>    | Potential Difference to \                                                                                                   | / <sub>RB</sub>         |        | 20  | 40   | 60    | mV      |

| Differential Gain Error         | DG                 |                                                                                                                             | NTSC 40 IRE Mod Ramp    |        | -   | 3    | -     | %       |

| Differential Phase Error        | DP                 | f <sub>C</sub> = 14.3 MSPS                                                                                                  |                         |        | -   | 1.5  | -     | Degrees |

| Sampling Delay                  | t <sub>SD</sub>    |                                                                                                                             |                         |        | -   | 0    | -     | ns      |

| Clamp Offset Voltage            | E <sub>OC</sub>    | $V_{IN} = DC, C_{IN} = 10 \mu F$<br>$t_{PCW} = 2.75 \mu s,$<br>$f_{C} = 14.3 \text{ MSPS},$<br>$f_{CLP} = 15.75 \text{kHz}$ | V <sub>REF</sub> = 0.5V |        | 0   | 20   | 40    | mV      |

|                                 |                    |                                                                                                                             | V <sub>REF</sub> = 2.5V |        | 0   | 20   | 40    | mV      |

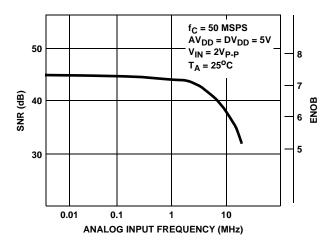

| Signal-To-Noise Ratio           | SNR                | f <sub>IN</sub> = 100kHz                                                                                                    |                         |        | -   | 45   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 500kHz                                                                                                    |                         |        | -   | 44   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 1MHz                                                                                                      |                         |        | -   | 44   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 3MHz                                                                                                      |                         |        | -   | 43   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 10MHz                                                                                                     |                         |        | -   | 38   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 25MHz                                                                                                     |                         |        | -   | 32   | -     | dB      |

| Spurious Free Dynamic           | SFDR               | f <sub>IN</sub> = 100kHz                                                                                                    |                         |        | -   | 51   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 500kHz                                                                                                    |                         |        | -   | 46   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 1MHz                                                                                                      |                         |        | -   | 49   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 3MHz                                                                                                      |                         |        | -   | 46   | -     | dB      |

|                                 |                    | f <sub>IN</sub> = 10MHz                                                                                                     |                         | -      | 45  | -    | dB    |         |

|                                 |                    | f <sub>IN</sub> = 25MHz                                                                                                     |                         | -      | 45  | -    | dB    |         |

### **Electrical Specifications** $f_C = 50 \text{ MSPS}, AV_{DD} = 5V, DV_{DD} = 3 \text{ to } 5.5V, V_{RB} = 0.5V, V_{RT} = 2.5V, T_A = 25^{\circ}C$ (Continued)

|                                                              | SYMBOL                                                                                         | TEST COM                                                                             | NOTES                             | MIN           | TYP                 | MAX  | UNITS |    |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------|---------------|---------------------|------|-------|----|

| DC CHARACTERISTICS $f_C =$                                   | 50 MSPS, A                                                                                     | $V_{DD} = 5V$ , $DV_{DD} = 5V$ or                                                    | $3.3V, V_{RB} = 0.5V, V_{RT}$     | $= 2.5V, T_A$ | = 25 <sup>o</sup> C |      |       |    |

| Supply Current                                               | I <sub>AD</sub> + I <sub>DD</sub>                                                              | NTSC Ramp,                                                                           | DV <sub>DD</sub> = 5V             |               | =                   | 25   | 36    | mA |

| Analog                                                       | I <sub>AD</sub>                                                                                | Wave Input,<br>CLE = 0V                                                              | DV <sub>DD</sub> = 3.3V           |               | -                   | 23   | 33    | mA |

| Digital                                                      | I <sub>DD</sub>                                                                                | OLL = UV                                                                             |                                   |               | =                   | 2    | 3     | mA |

| Reference Current                                            | I <sub>REF</sub>                                                                               |                                                                                      |                                   |               | 4.1                 | 5.4  | 7.7   | mA |

| Reference Resistance<br>(V <sub>RT</sub> - V <sub>RB</sub> ) | R <sub>REF</sub>                                                                               |                                                                                      |                                   |               | 260                 | 370  | 480   | Ω  |

| Self-Bias Voltage                                            | $V_{RB}$                                                                                       | Shorts V <sub>RTS</sub> and A <sub>VDD</sub>                                         |                                   | 0.52          | 0.56                | 0.60 | V     |    |

|                                                              | $V_{RT}$ - $V_{RB}$                                                                            | Shorts V <sub>RBS</sub> and A <sub>VSS</sub>                                         |                                   |               | 1.80                | 1.92 | 2.04  | V  |

| Input Capacitance                                            | C <sub>Al1</sub>                                                                               | $V_{IN}, V_{IN} = 1.5V + 0.07V$                                                      | <sup>'</sup> RMS                  |               | -                   | 15   | -     | pF |

|                                                              | C <sub>Al2</sub>                                                                               | V <sub>RTS</sub> , V <sub>RT</sub> , V <sub>RB</sub> , V <sub>RBS</sub>              | , V <sub>REF</sub>                |               | -                   | -    | 11    | pF |

|                                                              | C <sub>DIN</sub>                                                                               | TEST, CLK, CLP, CLE,                                                                 | ŌĒ                                |               | -                   | -    | 11    | pF |

| Output Capacitance                                           | C <sub>AO</sub>                                                                                | CCP                                                                                  |                                   |               | -                   | -    | 11    | pF |

|                                                              | C <sub>DO</sub>                                                                                | D0 to D7, TEST                                                                       |                                   |               | =                   | -    | 11    | pF |

| Digital Input Voltage                                        | V <sub>IH</sub>                                                                                | $AV_{DD} = 4.75 \text{ to } 5.25V,$                                                  |                                   | 2.2           | -                   | -    | V     |    |

|                                                              | V <sub>IL</sub>                                                                                | $DV_{DD} = 3 \text{ to } 5.5V, T_A =$                                                | -20°C to 75°C                     |               | -                   | -    | 0.8   | V  |

| Digital Input Current                                        | $I_{IH}$ $V_{I} = 0V \text{ to } AV_{DD},$ $T_{A} = 20^{\circ}\text{C to } 75^{\circ}\text{C}$ | CLK                                                                                  |                                   | -240          | -                   | 240  | μА    |    |

|                                                              |                                                                                                | $T_A = 20^{\circ}C \text{ to } 75^{\circ}C$                                          | TEST, CLP, CLE                    |               | -240                | -    | 40    | μА |

|                                                              |                                                                                                |                                                                                      | ŌĒ                                |               | -40                 | -    | 240   | μА |

| Digital Output Current                                       | Гон                                                                                            | $\overline{OE} = 0V$ , $DV_{DD} = 5V$                                                | $V_{OH} = DV_{DD} - 0.8V$         |               | -                   | -    | -2    | mA |

|                                                              | l <sub>OL</sub>                                                                                | $T_A = 20^{\circ} \text{C to } 75^{\circ} \text{C}$                                  | V <sub>OL</sub> = 0.4V            |               | 4                   | -    | -     | mA |

|                                                              | ГОН                                                                                            | OE = 0V                                                                              | $V_{OH} = DV_{DD} - 0.8V$         |               | -                   | -    | -1.2  | mA |

|                                                              | l <sub>OL</sub>                                                                                | $DV_{DD} = 3.3V$<br>$T_A = -20^{\circ}C \text{ to } 75^{\circ}C$                     | V <sub>OL</sub> = 0.4V            |               | 2.4                 | -    | -     | mA |

|                                                              | lozh                                                                                           | OE = 3V                                                                              | $V_{OH} = DV_{DD}$                |               | -40                 | -    | 40    | μΑ |

|                                                              | I <sub>OZL</sub>                                                                               | $DV_{DD} = 3 \text{ to } 5.5V$<br>$T_A = -20^{\circ}\text{C to } 75^{\circ}\text{C}$ | V <sub>OL</sub> = 0V              |               | -40                 | -    | 40    | μА |

| <b>TIMING</b> $f_C = 50 \text{ MSPS}, AV_{DD}$               | = 5V, DV <sub>DD</sub> =                                                                       | = 5V or 3.3V, V <sub>RB</sub> = 0.5V                                                 | $V_{RT} = 2.5V, T_A = 25^{\circ}$ | С             |                     |      |       |    |

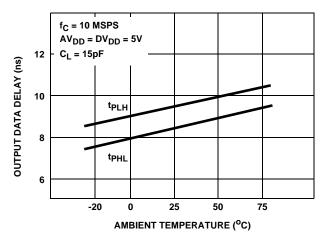

| Output Data Delay                                            | t <sub>PZH</sub>                                                                               | <u>CL</u> = 15pF                                                                     | $DV_{DD} = 5V$                    |               | 5.5                 | 9.5  | 12.0  | ns |

|                                                              | t <sub>PHL</sub> OE = 0V                                                                       | OE = 0V                                                                              |                                   |               |                     | 8.5  |       | ns |

|                                                              | t <sub>PLH</sub>                                                                               |                                                                                      | $DV_{DD} = 3.3V$                  |               | 4.3                 | 11.8 | 16.3  | ns |

|                                                              | t <sub>PHL</sub>                                                                               |                                                                                      |                                   |               |                     | 7.6  |       | ns |

| Three-State Output Enable                                    | t <sub>PZH</sub>                                                                               | $R_L = 1k\Omega$                                                                     | DV <sub>DD</sub> = 5V             |               | 2.5                 | 4.5  | 8.0   | ns |

| Time                                                         | t <sub>PZL</sub>                                                                               | C <sub>L</sub> = 15pF<br>OE = 3V→0V                                                  |                                   |               |                     | 6.0  |       | ns |

|                                                              | t <sub>PZH</sub>                                                                               | UE = 3V→UV                                                                           | DV <sub>DD</sub> = 3.3V           |               | 3.0                 | 7.0  | 9.0   | ns |

|                                                              | t <sub>PZL</sub>                                                                               |                                                                                      |                                   |               |                     | 5.0  | 1     | ns |

| Three-State Output Enable                                    | t <sub>PHZ</sub> , t <sub>PLZ</sub>                                                            | $R_L = 1k\Omega$ , $C_L = 15pF$                                                      | DV <sub>DD</sub> = 5V             |               | 3.5                 | 5.5  | 7.5   | ns |

| Time                                                         | t <sub>PZH</sub> , t <sub>PZL</sub>                                                            | OE = 3V→0V                                                                           | $DV_{DD} = 3.3V$                  |               | 2.5                 | 5.5  | 8.0   | ns |

| Clamp Pulse Width                                            | t <sub>CPW</sub>                                                                               | f <sub>C</sub> = 14.3MHz, C <sub>IN</sub> = 10                                       | μF for NTSC Wave                  | Note 4        | 1.75                | 2.75 | 3.75  | μS |

#### NOTES:

- 2. The offset voltage  $E_{OB}$  is a potential difference between  $V_{RB}$  and a point of position where the voltage drops equivalent to  $^{1}/_{2}$  LSB of the voltage when the output data changes from "00000000" to "00000001".  $E_{OT}$  is a potential difference between  $V_{RT}$  and a potential point where the voltage rises equivalent to  $^{1}/_{2}$  LSB of the voltage when the output data changes from "111111111" to "11111110".

- 3. The voltage of up to  $(AV_{DD} + 0.5V)$  can be input when  $DV_{DD} = 3.3V$ . But the output pin voltage is less than the  $DV_{DD}$  voltage. When the digital output is in the high impedance mode, the IC may be damaged by applying the voltage which is more than the  $(DV_{DD} + 0.5V)$  voltage to the digital output.

- 4. The clamp pulse width is for NTSC as an example. Adjust the rate to the clamp pulse cycle (1/15.75kHz for NTSC) for other processing systems to equal the values for NTSC.

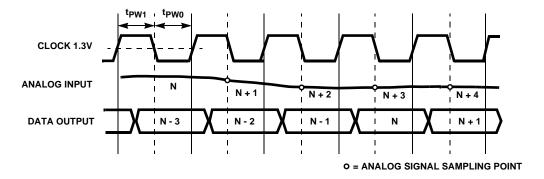

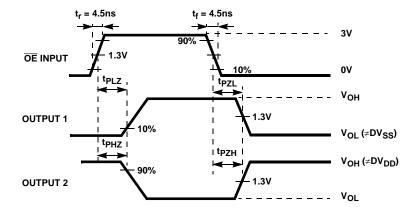

# **Timing Diagrams**

FIGURE 1A. TIMING CHART

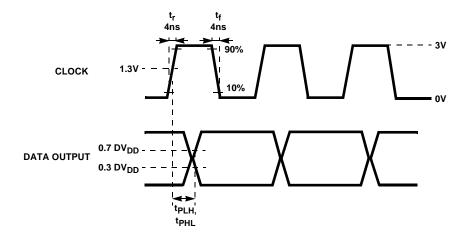

FIGURE 1B. TIMING CHART

FIGURE 1C. TIMING CHART

# Timing Diagrams (Continued)

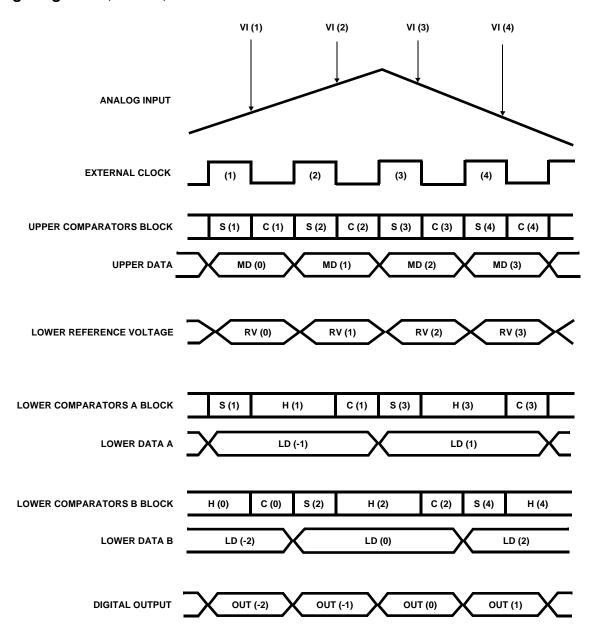

FIGURE 1D. TIMING CHART II

# Pin Descriptions

| PIN NO. | SYMBOL   | EQUIVALENT CIRCUIT                   | DESCRIPTION                  |

|---------|----------|--------------------------------------|------------------------------|

| 1 to 8  | D0 to D7 | DV <sub>DD</sub><br>DV <sub>SS</sub> | D0 (LSB) to D7 (MSB) Output. |

# Pin Descriptions (Continued)

| PIN NO.    | SYMBOL           | EQUIVALENT CIRCUIT                          | DESCRIPTION                                                                                                                                                                                                                       |

|------------|------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9          | TEST             | 9 DV <sub>DD</sub> DV <sub>SS</sub>         | Leave open for normal use.                                                                                                                                                                                                        |

| 10         | DV <sub>DD</sub> |                                             | Digital Power Supply +5V or +3.3V.                                                                                                                                                                                                |

| 11         | TEST             | AV <sub>DD</sub>                            | Leave open for normal use. Pull-up resistor is built in.                                                                                                                                                                          |

| 15         | CLP              | 11 5                                        | Input for the clamp pulse. Clamps the signal voltage during low interval. Pull-up resistor is built in.                                                                                                                           |

| 29         | CLE              | 29 AV <sub>SS</sub>                         | The clamp function is enabled when $\overline{\text{CLE}} = \text{Low}$ . The clamp function is off and the device functions as a normal A/D converter when $\overline{\text{CLE}} = \text{High}$ . Pull-up resistor is built in. |

| 12         | CLK              | 12 AV <sub>DD</sub>                         | Clock Input. Set to Low level when no clock is input.                                                                                                                                                                             |

| 13, 14, 32 | NC               |                                             |                                                                                                                                                                                                                                   |

| 16, 19, 20 | AV <sub>DD</sub> |                                             | Analog Power Supply +5V.                                                                                                                                                                                                          |

| 17         | V <sub>RTS</sub> | AV <sub>DD</sub>                            | Generates approximately +2.5V when shorted with AV <sub>DD</sub> .                                                                                                                                                                |

| 18         | $V_{RT}$         | ┆ <del>┈</del> ┸╗╒┸┇                        | Reference Voltage (Top).                                                                                                                                                                                                          |

| 24         | V <sub>RB</sub>  | (17)                                        | Reference Voltage (Bottom).                                                                                                                                                                                                       |

| 25         | VRBS             | 18 R <sub>REF</sub> 225 RB AV <sub>SS</sub> | Generates approximately +0.6V when shorted with AV <sub>SS</sub> .                                                                                                                                                                |

| 21         | VIN              | AV <sub>DD</sub> (21)  AV <sub>SS</sub>     | Analog Input.                                                                                                                                                                                                                     |

# Pin Descriptions (Continued)

| PIN NO. | SYMBOL            | EQUIVALENT CIRCUIT                    | DESCRIPTION                                                                                                                                 |

|---------|-------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 22, 23  | AV <sub>SS</sub>  |                                       | Analog Ground.                                                                                                                              |

| 26      | V <sub>RE</sub> F | AV <sub>DD</sub> 26  AV <sub>SS</sub> | Clamp Reference Voltage Input. Clamps so that the reference voltage and the input signal during clamp interval are equal.                   |

| 27      | CCP               | AV <sub>DD</sub> 27  AV <sub>SS</sub> | Integrates the clamp control voltage. The relationship between the changes in CCP voltage and in V <sub>IN</sub> voltage is positive phase. |

| 28, 31  | DV <sub>SS</sub>  |                                       | Digital Ground.                                                                                                                             |

| 30      | ŌĒ                | AV <sub>DD</sub> AV <sub>SS</sub>     | Data is output when $\overline{OE}$ = Low. Pins D0 to D7 are at high impedance when $\overline{OE}$ = High. Pull-down resistor is built in. |

# Digital Output

The following table shows the relationship between analog input voltage and digital output code.

| INPUT SIGNAL    |      | DIGITAL OUTPUT CODE |    |   |   |   |   |    |    |

|-----------------|------|---------------------|----|---|---|---|---|----|----|

| VOLTAGE         | STEP | M                   | SB |   |   |   |   | LS | SB |

| V <sub>RT</sub> | 0    | 1                   | 1  | 1 | 1 | 1 | 1 | 1  | 1  |

| •               | •    |                     |    |   |   | • |   |    |    |

| •               | •    |                     |    |   |   | • |   |    |    |

| •               | •    |                     |    | • |   |   |   |    |    |

| •               | 127  | 1                   | 0  | 0 | 0 | 0 | 0 | 0  | 0  |

| •               | 128  | 0                   | 1  | 1 | 1 | 1 | 1 | 1  | 1  |

| •               | •    |                     |    |   |   | • |   |    |    |

| •               | •    |                     |    |   |   | • |   |    |    |

| •               | •    | •                   |    |   |   |   |   |    |    |

| $V_{RB}$        | 255  | 0                   | 0  | 0 | 0 | 0 | 0 | 0  | 0  |

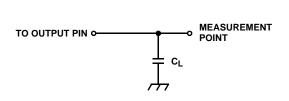

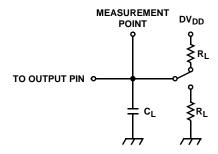

### **Electrical Specifications Measurement Circuits**

NOTE: C<sub>L</sub> includes capacitance of probes.

FIGURE 2. OUTPUT DATA DELAY MEASUREMENT CIRCUIT

FIGURE 3. THREE-STATE OUTPUT MEASUREMENT CIRCUIT

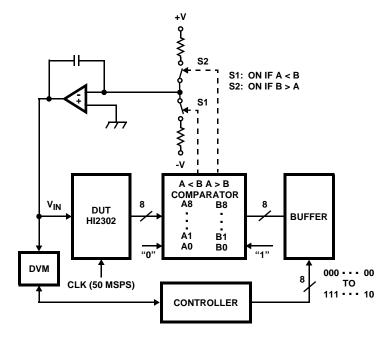

FIGURE 4. INTEGRAL NONLINEARITY ERROR/DIFFERENTIAL NONLINEARITY ERROR/OFFSET VOLTAGE TEST CIRCUIT

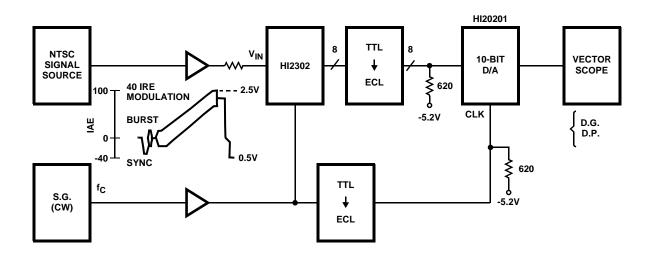

FIGURE 5. DIFFERENTIAL GAIN ERROR, DIFFERENTIAL PHASE ERROR TEST CIRCUIT

### Electrical Specifications Measurement Circuits (Continued)

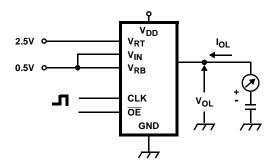

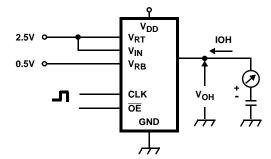

FIGURE 6. DIGITAL OUTPUT CURRENT TEST CIRCUIT

### **Operation** (See Block diagram and Timing Chart II)

- The HI2302 is a two-step parallel system A/D converter featuring a 4-bit upper comparator block and two lower comparator blocks of 4-bit each. The reference voltage that is equal to the voltage between V<sub>RT</sub> V<sub>RB</sub>/16 is constantly applied to the upper 4-bit comparator block. Voltage that corresponded to the upper data is fed through the reference supply to the lower 4-bit comparator block. Voltage that corresponded to the upper data is fed through the reference supply to the lower 4-bit comparator block. V<sub>RTS</sub> and V<sub>RBS</sub> pins serve for the self generation of V<sub>RT</sub> (reference voltage top) and V<sub>RB</sub> (reference voltage bottom), and they are also used as the sense pins as shown in the Application Circuit examples Figures 10 and 11.

- This IC uses an offset cancel type comparator which operates synchronously with an external clock. It features the following operating modes which are respectively indicated on the Timing Chart II with S, H, C symbols. That is input sampling (auto zero) mode, input hold mode and comparison mode.

- The operation of respective parts is as indicated in the Timing Chart II. For instance, input voltage VI (1) is sampled with the falling edge of the external clock (1) by means of the upper comparator block and the lower comparator A block.

The upper comparator block finalizes comparison data MD (1) with the rising edge of the external clock (2). Simultaneously the reference supply generates the lower reference voltage RV (1) that corresponded to the upper results. The lower comparator A Block finalizes comparison data LD (1) with the rising edge of the external clock (3). MD (1) and LD (1) are combined and output as Out (1) with the rising edge of the external clock (4). Accordingly there is a 2.5 clock delay from the analog input sampling point to the digital data output.

#### **Notes On Operation**

#### V<sub>DD</sub>, V<sub>SS</sub>

To reduce noise effects, separate the analog and digital systems close to the device. For both the digital and analog  $V_{DD}$  pins, use a ceramic capacitor of about  $0.1 \mu F$  set as close as possible to the pin to bypass to the respective GNDs.

#### Analog Input

Compared with the flash type A/D converter, the input capacitance of the analog input is rather small. However, it is necessary to conduct the drive with an amplifier featuring sufficient band and drive capability. When driving with an amplifier of low output impedance, parasitic oscillation may occur. That may be prevented by insetting a resistance of about 33 $\Omega$  in series between the amplifier output and A/D input. When the V<sub>IN</sub> signal of pin No. 21 is monitored, the kickback noise of clock is. However, this has no effect on the characteristics of A/D conversion.

#### · Clock Input

The clock line wiring should be as short as possible also, to avoid any interference with other signals, separate it from other circuits.

#### • Reference Input

Voltage V<sub>RT</sub> to V<sub>RB</sub> is compatible with the dynamic range of the analog input. Bypassing V<sub>RT</sub> and V<sub>RB</sub> pins to GND, by means of a capacitor about  $0.1\mu$ F, stable characteristics are obtained. By shorting V<sub>DD</sub> and V<sub>RTS</sub>, V<sub>SS</sub> and V<sub>RBS</sub> respectively, the self-bias function that generates V<sub>RT</sub> = about 2.5V and V<sub>RB</sub> = about 0.6V, is activated.

### Timing

Analog input is sampled with the falling edge of CLK and output as digital data synchronized with a delay of 2.5 clocks and with the following rising edge. The delay from the clock rising edge to the data output is about  $9ns (DV_{DD} = 5V)$ .

#### • OE Pin

$\begin{array}{l} \underline{\text{Pins 1 to 8}} \ (D_0 \ \text{to } D_7) \ \text{are in the output mode by leaving} \\ \overline{\text{OE}} \ \text{open or connecting it to DV}_{SS}, \ \text{and they are in the} \\ \text{high impedance mode by connecting it to DV}_{DD}. \end{array}$

# **Application Circuits**

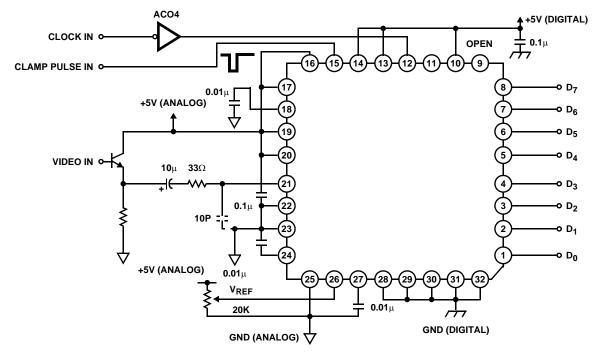

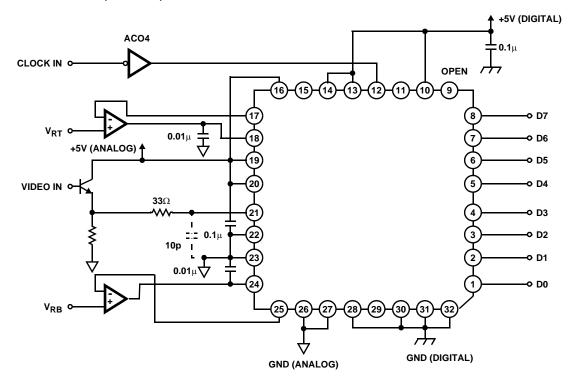

FIGURE 7. SINGLE +5V POWER SUPPLY WHEN CLAMP IS USED (SELF-BIAS USED)

#### NOTES:

- 5. The relationship between the changes in CCP voltage (Pin 27) and in  $V_{\mbox{\footnotesize{IN}}}$  voltage is positive phase.

- 6.  $\Delta V_{IN}/\Delta V_{CCP}$  = 3.0 (f<sub>S</sub> = 20 MSPS).

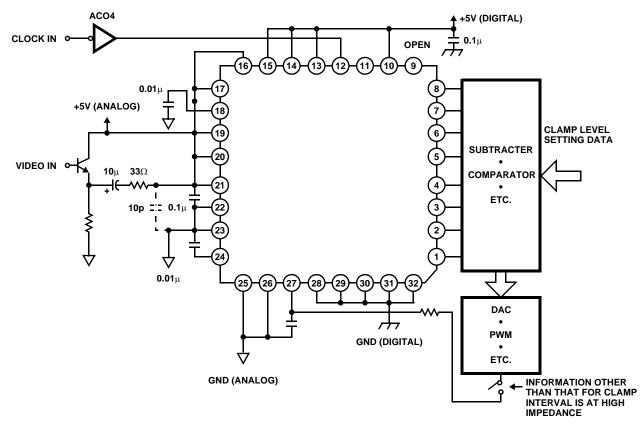

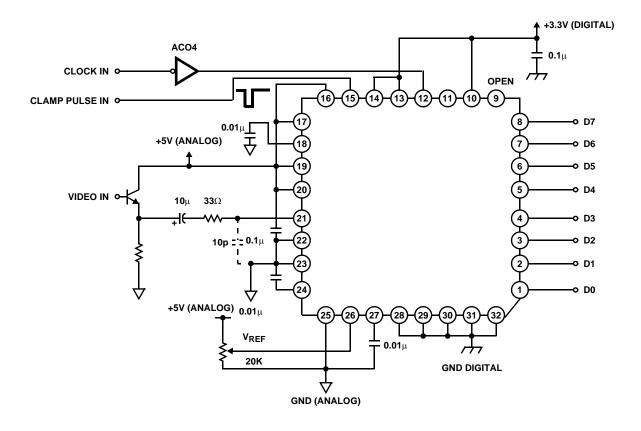

FIGURE 8. SINGLE +5V POWER SUPPLY DIGITAL CLAMP (SELF-BIAS USED)

# Application Circuits (Continued)

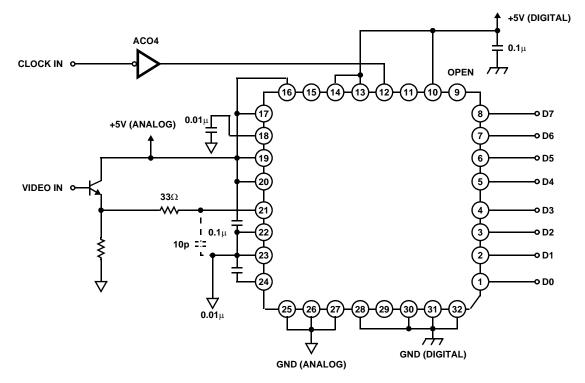

FIGURE 9. SINGLE +5V POWER SUPPLY WHEN CLAMP IS NOT USED (SELF-BIAS USED)

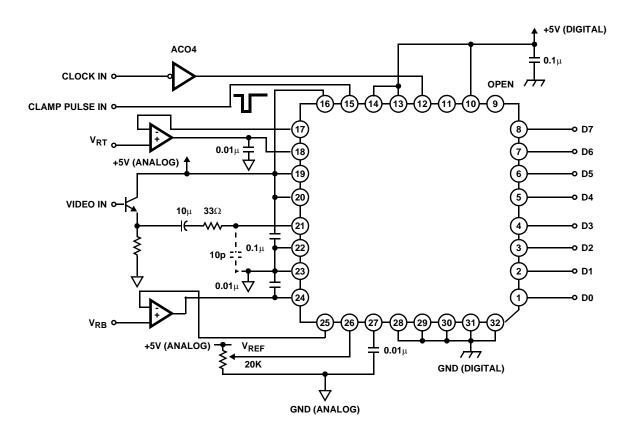

FIGURE 10. WHEN CLAMP IS USED (SELF-BIAS NOT USED)

# Application Circuits (Continued)

FIGURE 11. SINGLE +5V POWER SUPPLY WHEN CLAMP IS NOT USED (SELF-BIAS NOT USED)

FIGURE 12. DUAL +5V/+3.3V POWER SUPPLY WHEN CLAMP IS USED (SELF-BIAS USED)

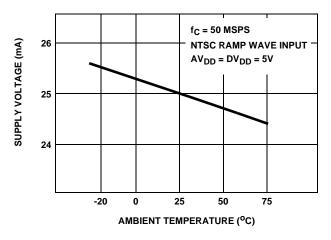

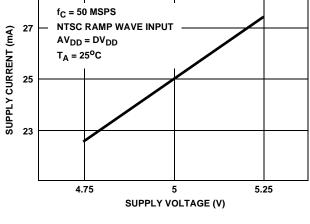

### **Typical Performance Curves**

FIGURE 13. AMBIENT TEMPERATURE vs SUPPLY CURRENT

FIGURE 14. SUPPLY VOLTAGE vs SUPPLY CURRENT

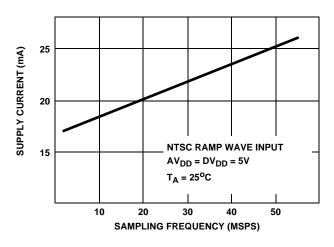

FIGURE 15. SAMPLING FREQUENCY vs SUPPLY CURRENT

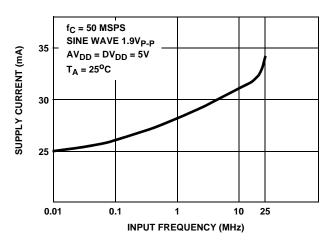

FIGURE 16. INPUT FREQUENCY vs SUPPLY CURRENT

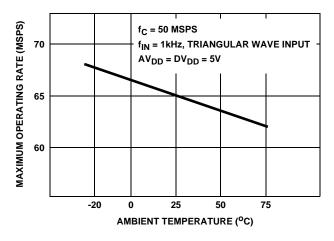

FIGURE 17. AMBIENT TEMPERATURE VS MAXIMUM OPERATING FREQUENCY

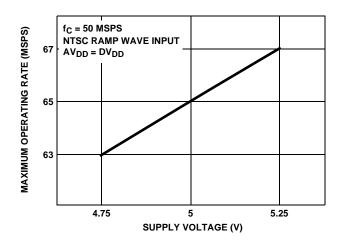

FIGURE 18. SUPPLY VOLTAGE VS MAXIMUM OPERATING FREQUENCY

### Typical Performance Curves (Continued)

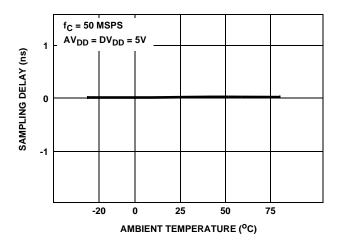

FIGURE 19. AMBIENT TEMPERATURE vs SAMPLING DELAY

FIGURE 21. ANALOG INPUT FREQUENCY vs SNR, EFFECTIVE NUMBER OF BITS (ENOB)

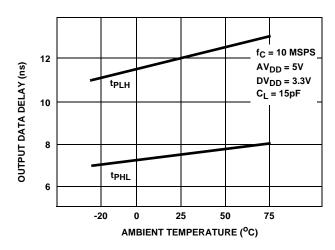

FIGURE 23. AMBIENT TEMPERATURE vs OUTPUT DATA DELAY

FIGURE 20. FULL SCALE INPUT BANDWIDTH

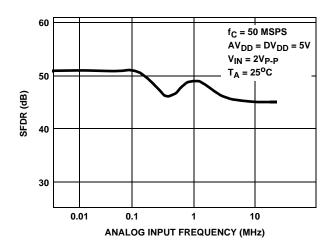

FIGURE 22. ANALOG INPUT FREQUENCY vs SFDR

FIGURE 24. AMBIENT TEMPERATURE vs OUTPUT DATA DELAY

### Typical Performance Curves (Continued)

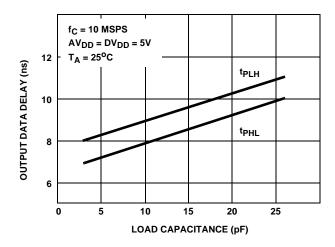

FIGURE 25. LOAD CAPACITANCE vs OUTPUT DATA DELAY

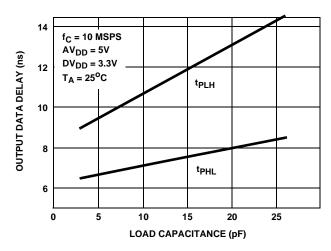

FIGURE 26. LOAD CAPACITANCE vs OUTPUT DATA DELAY

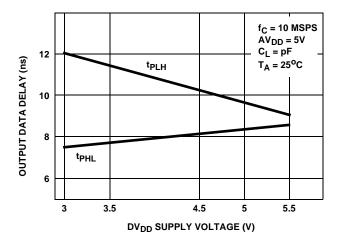

FIGURE 27.  $DV_{DD}$  SUPPLY VOLTAGE vs OUTPUT DATA DELAY

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com