#### 1. Features

- Write Protect Pin for Hardware Data Protection

- Utilizes Different Array Protection Compared to the AT24C02B

- Low-voltage and Standard-voltage Operation

- 1.8 ( $V_{CC}$  = 1.8V to 5.5V)

- Internally Organized 256 x 8 (2K)

- Two-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bidirectional Data Transfer Protocol

- 1 MHz (5V) and 400 kHz (1.8V, 2.5V, 2.7V) Clock Rate

- 8-byte Page

- Partial Page Writes Allowed

- Self-timed Write Cycle (5 ms Max)

- High Reliability

- Endurance: One Million Write Cycles

- Data Retention: 100 Years

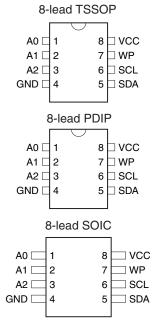

- 8-lead PDIP, 8-lead JEDEC SOIC and 8-lead TSSOP Packages

- Die Sales: Wafer Form, Tape and Reel, and Bumped Wafers

# 2. Description

The AT24HC02B provides 2048 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 256 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT24HC02B is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC and 8-lead TSSOP packages and is accessed via a two-wire serial interface. In addition, the entire family is available in 1.8V (1.8V to 5.5V) version.

**Table 2-1.** Pin Configuration

| Pin Name Function |                    |  |  |

|-------------------|--------------------|--|--|

| A0-A2             | Address Inputs     |  |  |

| SDA               | Serial Data        |  |  |

| SCL               | Serial Clock Input |  |  |

| WP                | Write Protect      |  |  |

# Two-wire Serial EEPROM

2K (256 x 8)

### AT24HC02B

Not Recommended for New Design.

Replaced by AT24HC02C.

Rev. 5134E-SEEPR-3/08

# **Absolute Maximum Ratings\***

| Operating Temperature                     | 55°C to +125°C |

|-------------------------------------------|----------------|

| Storage Temperature                       | 65°C to +150°C |

| Voltage on Any Pin with Respect to Ground | 1.0V to +7.0V  |

| Maximum Operating Voltage                 | 6.25V          |

| DC Output Current                         | 5.0 mA         |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

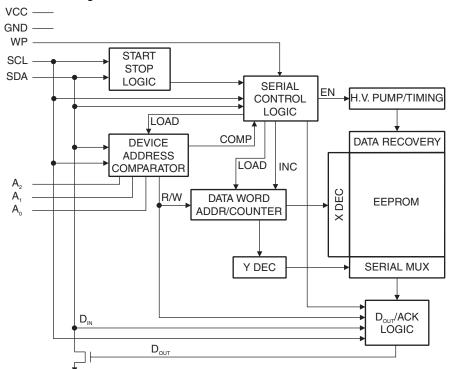

Figure 2-1. Block Diagram

### 3. Pin Description

**SERIAL CLOCK (SCL):** The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

**SERIAL DATA (SDA):** The SDA pin is bidirectional for serial data transfer. This pin is opendrain driven and may be wire-ORed with any number of other open-drain or open collector devices.

**DEVICE/PAGE ADDRESSES (A2, A1, A0):** The A2, A1 and A0 pins are device address inputs that must be hardwired for the AT24HC02B. As many as eight 2K devices may be addressed on a single bus system. (Device addressing is discussed in detail under *Device Addressing*, page 8).

**WRITE PROTECT (WP):** The AT24HC02B has a WP pin that provides hardware data protection. The WP pin allows normal read/write operations when connected to ground (GND). When the WP pin is connected to  $V_{CC}$ , the write protection feature is enabled and operates as shown.

Table 3-1.

Write Protect

|                    | Part of the Array Protected  |  |  |  |

|--------------------|------------------------------|--|--|--|

| WP Pin Status      | 24HC02B                      |  |  |  |

| At V <sub>CC</sub> | Upper Half (1K) Array        |  |  |  |

| At GND             | Normal Read/Write Operations |  |  |  |

# 4. Memory Organization

**AT24HC02B**, **2K SERIAL EEPROM**: The 2K is internally organized with 32 pages of 8 bytes each. Random word addressing requires an 8-bit data word address.

**Table 4-1.** Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from  $T_{AI} = 25$ °C, f = 1.0 MHz,  $V_{CC} = +1.8$ V

| Symbol           | Test Condition                                                             | Max | Units | Conditions     |

|------------------|----------------------------------------------------------------------------|-----|-------|----------------|

| C <sub>I/O</sub> | Input/Output Capacitance (SDA)                                             | 8   | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub>  | Input Capacitance (A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , SCL) | 6   | pF    | $V_{IN} = 0V$  |

Note: 1. This parameter is characterized and is not 100% tested.

Table 4-2. DC Characteristics

Applicable over recommended operating range from:  $T_{Al} = -40$ °C to +85°C,  $V_{CC} = +1.8$ V to +5.5V (unless otherwise noted)

| Symbol           | Parameter                               | Test Condition                                       | Min                   | Тур  | Max                   | Units |

|------------------|-----------------------------------------|------------------------------------------------------|-----------------------|------|-----------------------|-------|

| V <sub>CC1</sub> | Supply Voltage                          |                                                      | 1.8                   |      | 5.5                   | V     |

| V <sub>CC2</sub> | Supply Voltage                          |                                                      | 2.5                   |      | 5.5                   | ٧     |

| V <sub>CC3</sub> | Supply Voltage                          |                                                      | 2.7                   |      | 5.5                   | V     |

| V <sub>CC4</sub> | Supply Voltage                          |                                                      | 4.5                   |      | 5.5                   | V     |

| I <sub>cc</sub>  | Supply Current V <sub>CC</sub> = 5.0V   | READ at 100 kHz                                      |                       | 0.4  | 1.0                   | mA    |

| I <sub>CC</sub>  | Supply Current V <sub>CC</sub> = 5.0V   | WRITE at 100 kHz                                     |                       | 2.0  | 3.0                   | mA    |

| I <sub>SB1</sub> | Standby Current V <sub>CC</sub> = 1.8V  | $V_{IN} = V_{CC}$ or $V_{SS}$                        |                       | 0.6  | 3.0                   | μΑ    |

| I <sub>SB2</sub> | Standby Current V <sub>CC</sub> = 2.5V  | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub> |                       | 1.4  | 4.0                   | μΑ    |

| I <sub>SB3</sub> | Standby Current V <sub>CC</sub> = 2.7V  | $V_{IN} = V_{CC}$ or $V_{SS}$                        |                       | 1.6  | 4.0                   | μΑ    |

| I <sub>SB4</sub> | Standby Current V <sub>CC</sub> = 5.0V  | $V_{IN} = V_{CC}$ or $V_{SS}$                        |                       | 8.0  | 18.0                  | μΑ    |

| I <sub>LI</sub>  | Input Leakage Current                   | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub> |                       | 0.10 | 3.0                   | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current                  | $V_{OUT} = V_{CC} \text{ or } V_{SS}$                |                       | 0.05 | 3.0                   | μΑ    |

| V <sub>IL</sub>  | Input Low Level (1)                     |                                                      | -0.6                  |      | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub>  | Input High Level (1)                    |                                                      | V <sub>CC</sub> x 0.7 |      | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL2</sub> | Output Low Level V <sub>CC</sub> = 3.0V | I <sub>OL</sub> = 2.1 mA                             |                       |      | 0.4                   | V     |

| V <sub>OL1</sub> | Output Low Level V <sub>CC</sub> = 1.8V | I <sub>OL</sub> = 0.15 mA                            |                       |      | 0.2                   | V     |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

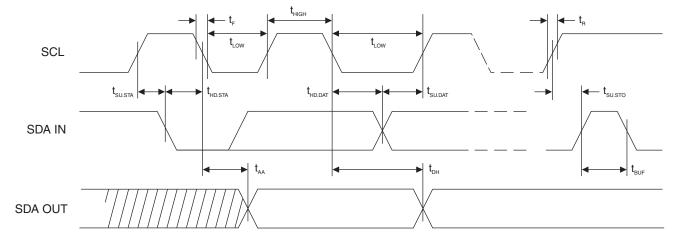

Table 4-3. AC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{CC} = +1.8\text{V}$  to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted)

|                          |                                                               | 1.8, 2 | 1.8, 2.5, 2.7 |      | volt |              |  |

|--------------------------|---------------------------------------------------------------|--------|---------------|------|------|--------------|--|

| Symbol                   | Parameter                                                     | Min    | Max           | Min  | Max  | Units        |  |

| f <sub>SCL</sub>         | Clock Frequency, SCL                                          |        | 400           |      | 1000 | kHz          |  |

| t <sub>LOW</sub>         | Clock Pulse Width Low                                         | 1.2    |               | 0.4  |      | μs           |  |

| t <sub>HIGH</sub>        | Clock Pulse Width High                                        | 0.6    |               | 0.4  |      | μs           |  |

| t <sub>l</sub>           | Noise Suppression Time                                        |        | 50            |      | 40   | ns           |  |

| t <sub>AA</sub>          | Clock Low to Data Out Valid                                   | 0.1    | 0.9           | 0.05 | 0.55 | μs           |  |

| t <sub>BUF</sub>         | Time the bus must be free before a new transmission can start | 1.2    |               | 0.5  |      | μѕ           |  |

| t <sub>HD.STA</sub>      | Start Hold Time                                               | 0.6    |               | 0.25 |      | μs           |  |

| t <sub>SU.STA</sub>      | Start Setup Time                                              | 0.6    |               | 0.25 |      | μs           |  |

| t <sub>HD.DAT</sub>      | Data In Hold Time                                             | 0      |               | 0    |      | μs           |  |

| t <sub>SU.DAT</sub>      | Data In Setup Time                                            | 100    |               | 100  |      | ns           |  |

| t <sub>R</sub>           | Inputs Rise Time <sup>(1)</sup>                               |        | 0.3           |      | 0.3  | μs           |  |

| t <sub>F</sub>           | Inputs Fall Time <sup>(1)</sup>                               |        | 300           |      | 100  | ns           |  |

| t <sub>su.sto</sub>      | Stop Setup Time                                               | 0.6    |               | .25  |      | μs           |  |

| t <sub>DH</sub>          | Data Out Hold Time                                            | 50     |               | 50   |      | ns           |  |

| t <sub>WR</sub>          | Write Cycle Time                                              |        | 5             |      | 5    | ms           |  |

| Endurance <sup>(1)</sup> | 5.0V, 25°C, Byte Mode                                         |        | 1 Million     |      |      | Write Cycles |  |

Note: 1. This parameter is ensured by characterization only.

### 5. Device Operation

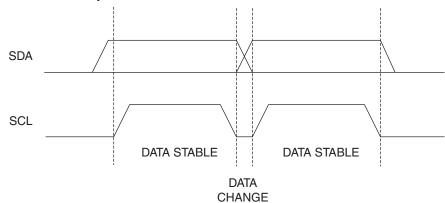

**CLOCK and DATA TRANSITIONS:** The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 5-1). Data changes during SCL high periods will indicate a start or stop condition as defined below.

Figure 5-1. Data Validity

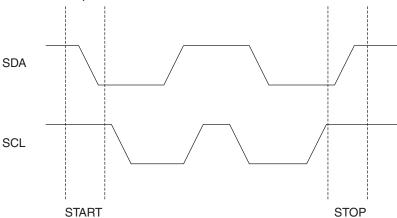

**START CONDITION:** A high-to-low transition of SDA with SCL high is a start condition that must precede any other command (see Figure 5-2).

Figure 5-2. Start and Stop Definition

**STOP CONDITION:** A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 5-2).

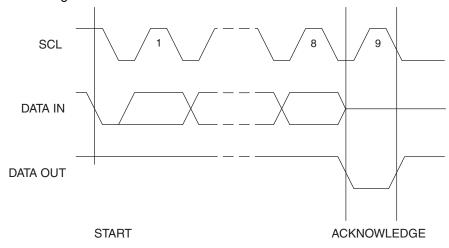

**ACKNOWLEDGE:** All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a "0" to acknowledge that it has received each word. This happens during the ninth clock cycle.

**STANDBY MODE:** The AT24HC02B features a low-power standby mode that is enabled: (a) upon power-up and (b) after the receipt of the Stop bit and the completion of any internal operations.

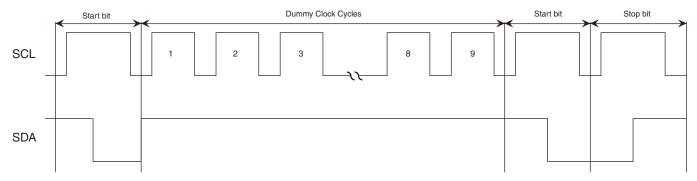

**2-WIRE SOFTWARE RESET:** After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps: (a) Clock up to 9 cycles, (b) Look for SDA high in each cycle while SCL is high, (c) Create a start condition as SDA is high. The device is ready for next communication after above steps have been completed.

Figure 5-3. Software Reset

Figure 5-4. Bus Timing

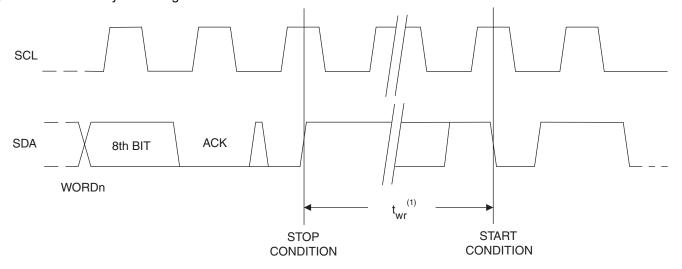

Figure 5-5. Write Cycle Timing

Notes: 1. The write cycle time t<sub>WB</sub> is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.

Figure 5-6. Output Acknowledge

# 6. Device Addressing

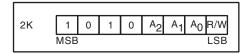

The 2K EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or write operation, as shown in Figure 6-1.

Figure 6-1. Device Address

The device address word consists of a mandatory "1", "0" sequence for the first four most significant bits as shown. This is common to all the EEPROM devices.

The next three bits are the A2, A1 and A0 device address bits for the 2K EEPROM. These three bits must compare to their corresponding hardwired input pins.

The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high, and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will output a "0". If a compare is not made, the chip will return to a standby state.

### 7. Write Operations

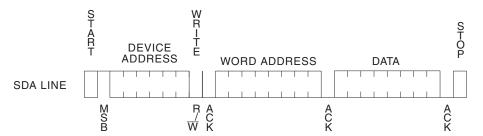

**BYTE WRITE:** A write operation requires an 8-bit data word address following the device address word and acknowledgement. Upon receipt of this address, the EEPROM will again respond with a "0" and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a "0" and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time, the EEPROM enters an internally-timed write cycle,  $t_{WR}$ , to the nonvolatile memory. All inputs are disabled during this write cycle, and the EEPROM will not respond until the write is complete, see Figure 7-1 on page 9.

Figure 7-1. Byte Write

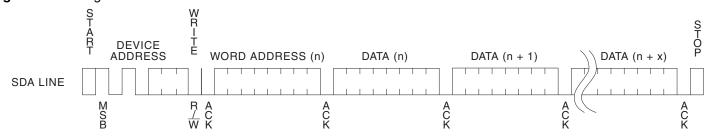

PAGE WRITE: The 2K EEPROM is capable of an 8-byte page write.

A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven (2K) more data words. The EEPROM will respond with a "0" after each data word received. The microcontroller must terminate the page write sequence with a stop condition, see Figure 7-2.

Figure 7-2. Page Write

The data word address lower three (2K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (2K) data words are transmitted to the EEPROM, the data word address will "roll over" and previous data will be overwritten.

**ACKNOWLEDGE POLLING:** Once the internally-timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a "0" allowing the read or write sequence to continue.

### 8. Read Operations

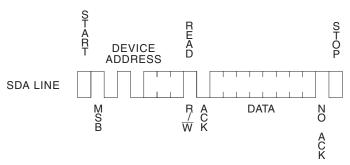

Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to "1". There are three read operations: current address read, random address read and sequential read.

**CURRENT ADDRESS READ:** The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.

Once the device address with the read/write select bit set to "1" is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input "0" but does generate a following stop condition, see Figure 8-1.

Figure 8-1. Current Address Read

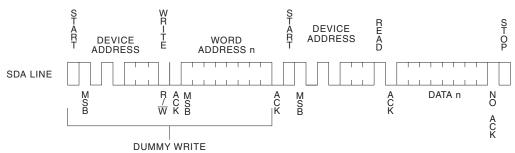

**RANDOM READ:** A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a "0" but does generate a following stop condition, see Figure 8-2.

Figure 8-2. Random Read

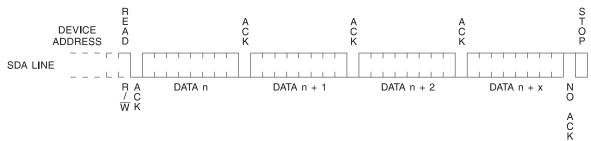

**SEQUENTIAL READ:** Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a "0" but does generate a following stop condition, see Figure 8-3.

Figure 8-3. Sequential Read

# 9. AT24HC02B Ordering Information

| Ordering Code                                       | Voltage | Package  | Operation Range                           |

|-----------------------------------------------------|---------|----------|-------------------------------------------|

| AT24HC02B-PU (Bulk form only)                       | 1.8     | 8P3      |                                           |

| AT24HC02BN-SH-B <sup>(1)</sup> (NiPdAu Lead Finish) | 1.8     | 8S1      | Lead-free/Halogen-free/                   |

| AT24HC02BN-SH-T <sup>(2)</sup> (NiPdAu Lead Finish) | 1.8     | 8S1      | Industrial Temperature<br>(–40°C to 85°C) |

| AT24HC02B-TH-B <sup>(1)</sup> (NiPdAu Lead Finish)  | 1.8     | 8A2      | ( 10 0 10 00 0)                           |

| AT24HC02B-TH-T <sup>(2)</sup> (NiPdAu Lead Finish)  | 1.8     | 8A2      |                                           |

| AT24HC02B-W-11 <sup>(3)</sup>                       | 1.8     | Die Sale | Industrial Temperature<br>(-40°C to 85°C) |

Notes: 1. "-B" denotes bulk.

- 2. "-T" denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel.

- 3. Available in tape and reel and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial Interface Marketing.

|         | Package Type                                                           |  |  |  |  |

|---------|------------------------------------------------------------------------|--|--|--|--|

| 8P3     | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                |  |  |  |  |

| 8S1     | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)      |  |  |  |  |

| 8A2     | 8-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP) |  |  |  |  |

| Options |                                                                        |  |  |  |  |

| -1.8    | Low Voltage (1.8V to 5.5V)                                             |  |  |  |  |

# 10. Part marking scheme

# 10.1 8-PDIP

| TOP | P MARK |      |      | Seal Year |     |    |      |      |

|-----|--------|------|------|-----------|-----|----|------|------|

|     |        |      |      |           |     | -  | Seal | Week |

|     |        |      |      |           |     | 1  |      |      |

|     |        |      |      |           |     |    |      |      |

|     | A      | T    | M    | L         | Н   | Y  | M    | W    |

|     |        |      |      |           |     |    |      |      |

|     | Н      | 2    | В    |           | 1   |    |      |      |

|     | -      |      |      |           |     |    |      |      |

|     | *      | Lot  | Num  | nber      |     |    |      |      |

|     | -      |      |      |           |     |    |      |      |

|     |        |      |      |           |     |    |      |      |

|     | Pin :  | 1 In | dica | tor       | (Do | t) |      |      |

| Y =        | SEAL | YEAR |      | WW = | = 5 | SEAL ' | WEEK |  |

|------------|------|------|------|------|-----|--------|------|--|

| 6 <b>:</b> | 2006 | 0:   | 2010 | 02   | =   | Week   | 2    |  |

| 7:         | 2007 | 1:   | 2011 | 04   | =   | Week   | 4    |  |

| 8:         | 2008 | 2:   | 2012 | ::   | :   | ::::   | :    |  |

| 9:         | 2009 | 3:   | 2013 | ::   | :   | ::::   | ::   |  |

|            |      |      |      | 50   | =   | Week   | 50   |  |

|            |      |      |      | 52   | =   | Week   | 52   |  |

Lot Number to Use ALL Characters in Marking

#### BOTTOM MARK

No Bottom Mark

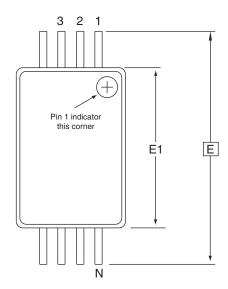

### 10.2 8-SOIC

| TOP MARK               |     | Yea<br>Seal | r<br>Week |

|------------------------|-----|-------------|-----------|

|                        | 1   | 1           | I         |

| <br>A T M L H          |     |             |           |

|                        |     |             |           |

| н 2 в 1                | -   |             |           |

| <br>* Lot Number       |     |             |           |

|                        |     |             |           |

| <br>Pin 1 Indicator (D | ot) |             |           |

| Υ =        | SEAL | YEAR |      | WW = | = 5 | SEAL 1 | WEEF | ζ |

|------------|------|------|------|------|-----|--------|------|---|

| 6 <b>:</b> | 2006 | 0:   | 2010 | 02   | =   | Week   | 2    |   |

| 7:         | 2007 | 1:   | 2011 | 04   | =   | Week   | 4    |   |

| 8:         | 2008 | 2:   | 2012 | ::   | :   | ::::   | :    |   |

| 9:         | 2009 | 3:   | 2013 | ::   | :   | ::::   | ::   |   |

|            |      |      |      | 50   | =   | Week   | 50   |   |

|            |      |      |      | 52   | =   | Week   | 52   |   |

Lot Number to Use ALL Characters in Marking

#### BOTTOM MARK

No Bottom Mark

#### 10.3 8-TSSOP

#### TOP MARK

####

#### BOTTOM MARK

# 11. Packaging Information

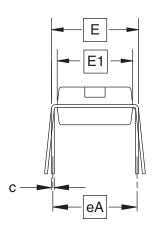

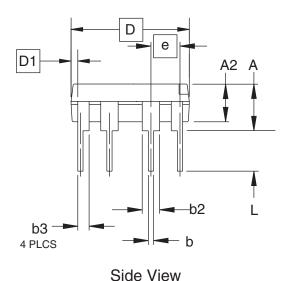

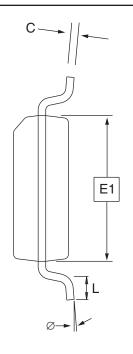

#### 11.1 8P3 - PDIP

Top View

**End View**

#### **COMMON DIMENSIONS**

(Unit of Measure = inches)

| SYMBOL | MIN       | NOM   | MAX   | NOTE |

|--------|-----------|-------|-------|------|

| Α      | ı         | _     | 0.210 | 2    |

| A2     | 0.115     | 0.130 | 0.195 |      |

| b      | 0.014     | 0.018 | 0.022 | 5    |

| b2     | 0.045     | 0.060 | 0.070 | 6    |

| b3     | 0.030     | 0.039 | 0.045 | 6    |

| С      | 0.008     | 0.010 | 0.014 |      |

| D      | 0.355     | 0.365 | 0.400 | 3    |

| D1     | 0.005     | _     | _     | 3    |

| Е      | 0.300     | 0.310 | 0.325 | 4    |

| E1     | 0.240     | 0.250 | 0.280 | 3    |

| е      | 0.100 BSC |       |       |      |

| eA     | 0.300 BSC |       |       | 4    |

| L      | 0.115     | 0.130 | 0.150 | 2    |

Notes:

- 1. This drawing is for general information only; refer to JEDEC Drawing MS-001, Variation BA, for additional information.

- 2. Dimensions A and L are measured with the package seated in JEDEC seating plane Gauge GS-3.

- 3. D. D1 and E1 dimensions do not include mold Flash or protrusions. Mold Flash or protrusions shall not exceed 0.010 inch.

- 4. E and eA measured with the leads constrained to be perpendicular to datum.

- 5. Pointed or rounded lead tips are preferred to ease insertion.

- 6. b2 and b3 maximum dimensions do not include Dambar protrusions. Dambar protrusions shall not exceed 0.010 (0.25 mm).

01/09/02

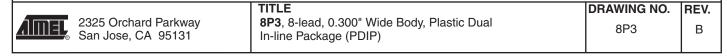

### 11.2 8S1 - JEDEC SOIC

Top View

Side View

**End View**

# **COMMON DIMENSIONS** (Unit of Measure = mm)

| SYMBOL | MIN      | NOM | MAX  | NOTE |

|--------|----------|-----|------|------|

| А      | 1.35     | _   | 1.75 |      |

| A1     | 0.10     | -   | 0.25 |      |

| b      | 0.31     | _   | 0.51 |      |

| С      | 0.17     | -   | 0.25 |      |

| D      | 4.80     | _   | 5.00 |      |

| E1     | 3.81     | _   | 3.99 |      |

| Е      | 5.79     | _   | 6.20 |      |

| е      | 1.27 BSC |     |      |      |

| L      | 0.40     | _   | 1.27 |      |

| Ø      | 0°       | _   | 8°   |      |

Note: These drawings are for general information only. Refer to JEDEC Drawing MS-012, Variation AA for proper dimensions, tolerances, datums, etc.

10/7/03

| AIMEL | 0 1 0 1 00 | 8 <b>S</b> 1 |

|-------|------------|--------------|

|       |            |              |

| TITLE                                             |   |

|---------------------------------------------------|---|

| 8S1, 8-lead (0.150" Wide Body), Plastic Gull Wing | g |

| Small Outline (JEDEC SOIC)                        | _ |

| DRAWING NO. | REV. |

|-------------|------|

| 8S1         | В    |

|             |      |

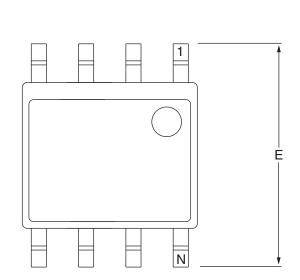

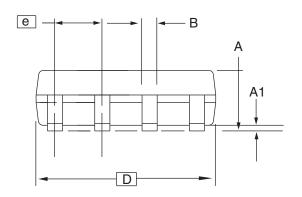

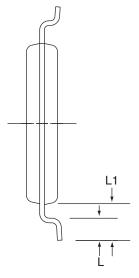

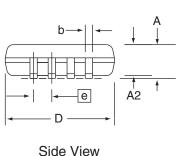

#### 11.3 8A2 - TSSOP

Top View

**End View**

#### **COMMON DIMENSIONS**

(Unit of Measure = mm)

| SYMBOL | MIN      | NOM      | MAX  | NOTE |

|--------|----------|----------|------|------|

| D      | 2.90     | 3.00     | 3.10 | 2, 5 |

| E      |          | 6.40 BSC |      |      |

| E1     | 4.30     | 4.40     | 4.50 | 3, 5 |

| Α      | _        | _        | 1.20 |      |

| A2     | 0.80     | 1.00     | 1.05 |      |

| b      | 0.19     | _        | 0.30 | 4    |

| е      | 0.65 BSC |          |      |      |

| L      | 0.45     | 0.60     | 0.75 |      |

| L1     | 1.00 REF |          |      |      |

Notes: 1. This drawing is for general information only. Refer to JEDEC Drawing MO-153, Variation AA, for proper dimensions, tolerances, datums, etc.

- 2. Dimension D does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15 mm (0.006 in) per side.

- 3. Dimension E1 does not include inter-lead Flash or protrusions. Inter-lead Flash and protrusions shall not exceed 0.25 mm (0.010 in) per side.

- 4. Dimension b does not include Dambar protrusion. Allowable Dambar protrusion shall be 0.08 mm total in excess of the b dimension at maximum material condition. Dambar cannot be located on the lower radius of the foot. Minimum space between protrusion and adjacent lead is 0.07 mm.

- 5. Dimension D and E1 to be determined at Datum Plane H.

5/30/02

# 12. Revision History

| Doc. Rev. | Date   | Comments                                                                                                                                                                     |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5134E     | 9/2013 | NRND. Replaced by AT24HC02B                                                                                                                                                  |

| 5134E     | 3/2008 | Added part marking scheme Updated to new template                                                                                                                            |

| 5134D     | 4/2007 | Removed reference to Waffle Pack on page 1 Added lines to Ordering Code table Shrink Pin Diagram; Change to Table 5; Added Two-Wire Software Reset; Removed LSB from figures |

| 5134C     | 3/2007 | Pg. 12 - Change to new catalog part number scheme.                                                                                                                           |

| 5134B     | 9/2006 | Revision history implemented; Added 'Preliminary' status to datasheet.                                                                                                       |

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-

Yvelines Cedex France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033

Japan Tel: (81) 3-3523-3551

Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support

s\_eeprom@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

AT24HC02BN-SH-B AT24HC02B-TH-B AT24HC02B-TH-T AT24HC02BN-SH-T AT24HC02B-PU