# Isolated Dual Channel IGBT/MOSFET Gate Driver

NCD57252, NCD57253, NCD57255, NCD57256, NCV57252, NCV57253, NCV57255, NCV57256

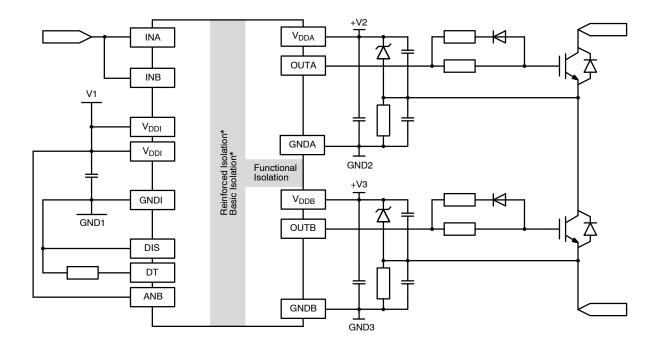

NCx5725y are high–current two channel isolated IGBT/MOSFET gate drivers with 2.5 or 5 kV $_{rms}$ \* internal galvanic isolation from input to each output and functional isolation between the two output channels. The device accepts 3.3 V to 20 V bias voltage and signal levels on the input side and up to 32 V bias voltage on the output side. The device accepts complementary inputs and offers separate pins for Disable and Dead Time control for system design convenience. Drivers are available in wide body SOIC–16 and narrow body SOIC–16 package.

#### **Features**

- High Peak Output Current (±6.5 A\*, ±3.5 A\*)

- Configurable as a Dual Low-Side or Dual High-Side or Half-Bridge Driver

- Programmable Overlap or Dead Time control

- Disable Pin to Turn Off Outputs for Power Sequencing

- ANB Function to Offer Flexibility to Set up the Driver as Half-bridge Driver Operating with a Single Input Signal

- IGBT/MOSFET Gate Clamping during Short Circuit

- Short Propagation Delays with Accurate Matching

- Tight UVLO Thresholds on all Power Supplies

- 3.3 V, 5 V, and 15 V Logic Input

- 2.5 or 5 kV<sub>rms</sub>\* Galvanic Isolation from Input to each Output and 1.5 kV<sub>rms</sub> Differential Voltage between Output Channels

- 1200 V Working Voltage (per VDE0884–11 Requirements)

- High Common Mode Transient Immunity

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- This Device is Pb–Free, Halogen Free/BFR Free and is RoHS Compliant

#### **Typical Applications**

- EV Chargers

- Motor Control

- Uninterruptible Power Supplies (UPS)

- Industrial Power Supplies

- Solar Inverters

- Automotive Applications

6 WB D SUFFIX 1G-03 CASE 751B-05

#### MARKING DIAGRAMS

5725y = Specific Device Code

y = 2, 3, 5 or 6

A = Assembly Location

WL = Wafer Lot YY, Y = Year

WW = Work Week

G = Pb-Free Package

(See page 21)

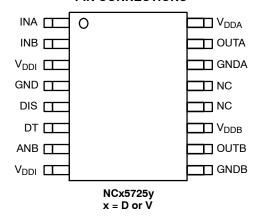

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 21 of this data sheet.

<sup>\*</sup>Depends on package variant, see Page 6, 21.

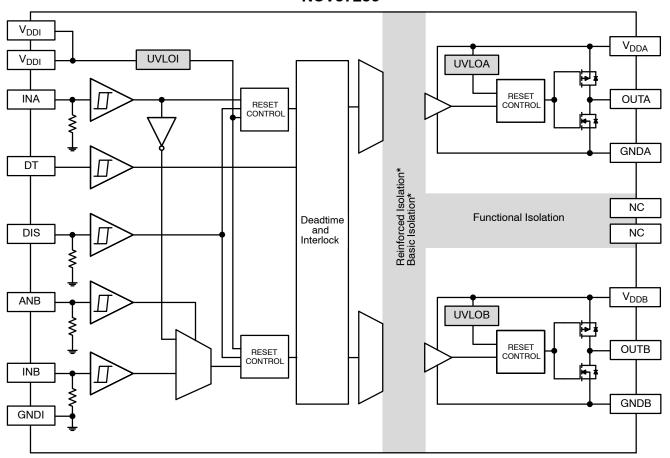

Figure 1. Simplified Block Diagram

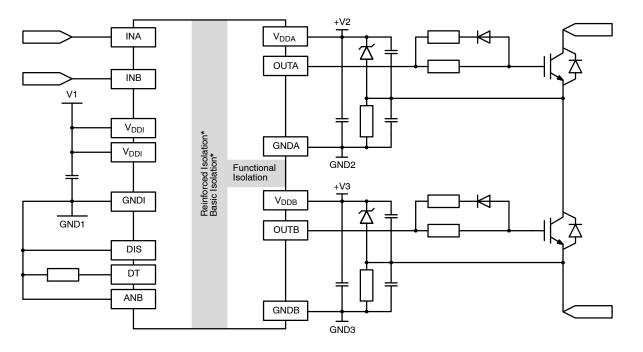

Figure 2. Typical Application, High and Low Side IGBT Gate Drive

<sup>\*</sup>Depends on package variant, see Page 6, 21.

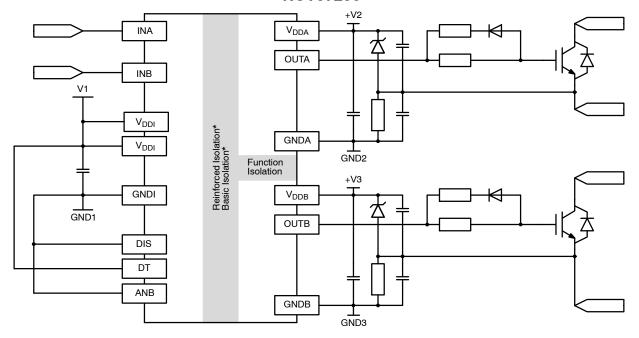

Figure 3. Typical Application, Two Channels IGBT Gate Drive

Figure 4. Typical Application, High and Low Side IGBT Gate Drive with PWM Controller

<sup>\*</sup>Depends on package variant, see Page 6, 21.

#### **Table 1. FUNCTION DESCRIPTION**

| Pin Name   | No.          | I/O        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INA        | 1            | Input      | A non-inverting gate driver input that defines OUTA. It has an equivalent pull-down resistor of 125 k $\Omega$ to ensure that output is low in the absence of an input signal.                                                                                                                                                                                                                                                                                                                                                                |

|            |              |            | A positive or negative going pulse with pulse width longer than maximum value of $t_{\rm MIN2}$ is required at INA before OUTA reacts.                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |              |            | The input logic levels scale with $V_{DDI}$ up to $V_{DDI}$ = 5 V. With $V_{DDI}$ above 5 V the input logic levels stay the same as for $V_{DDI}$ = 5 V. Maximum voltage on this pin is $V_{DDI}$ .                                                                                                                                                                                                                                                                                                                                           |

| INB        | 2            | Input      | A non–inverting gate driver input that defines OUTB. It has an equivalent pull–down resistor of 125 k $\Omega$ to ensure that output is low in the absence of an input signal.                                                                                                                                                                                                                                                                                                                                                                |

|            |              |            | A positive or negative going pulse with pulse width longer than maximum value of $t_{\text{MIN2}}$ is required at INB before OUTB reacts.                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |              |            | The input logic levels scale with $V_{DDI}$ up to $V_{DDI}$ = 5 V. With $V_{DDI}$ above 5 V the input logic levels stay the same as for $V_{DDI}$ = 5 V. Maximum voltage on this pin is $V_{DDI}$ .                                                                                                                                                                                                                                                                                                                                           |

| $V_{DDI}$  | 3, 8         | Power      | Low voltage side power supply. A good quality bypassing capacitor is required from this pin to GNDI and should be placed close to the pins for best results.                                                                                                                                                                                                                                                                                                                                                                                  |

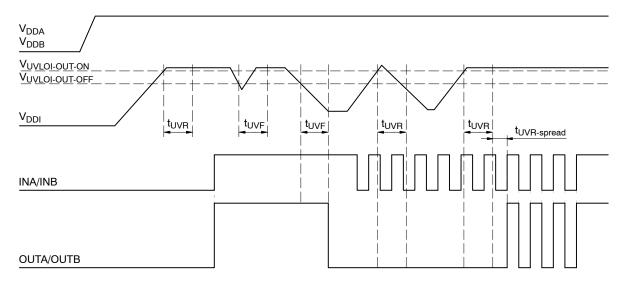

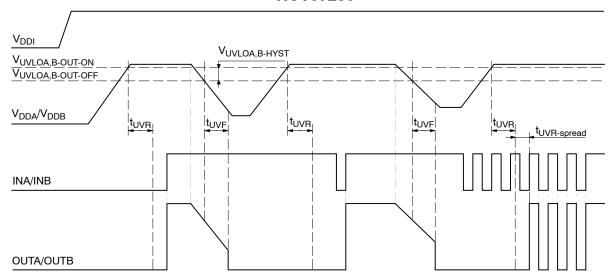

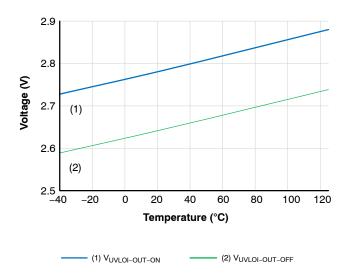

|            |              |            | The under voltage lockout (UVLOI) circuit enables the device to operate at power on when a typical supply voltage higher than V <sub>UVLOI-OUT-ON</sub> is present.  Please see Figure 7 and 8 for more details.                                                                                                                                                                                                                                                                                                                              |

| GNDI       | 4            | Power      | Low voltage side ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

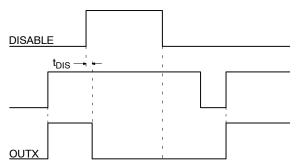

| DIS        | 5            | Input      | A high level on disable pin turns both OUTA and OUTB low simultaneously regardless of the states of INA, INB, DT and ANB. Minimum pulse width filter and propagation delays apply. It has an equivalent pull–down resistor of 125 k $\Omega$ to ensure that OUTA and OUTB react to INA, INB, DT and ANB in the absence of an input signal.                                                                                                                                                                                                    |

|            |              |            | The input logic levels scale with $V_{DDI}$ up to $V_{DDI}$ = 5 V. With $V_{DDI}$ above 5 V the input logic levels stay the same as for $V_{DDI}$ = 5 V. Maximum voltage on this pin is $V_{DDI}$ .                                                                                                                                                                                                                                                                                                                                           |

| DT         | 6            | Input      | A deadtime pin is used to configure the two outputs sequence. The deadtime $(t_{DT})$ and interlocking logic between INA and INB is defined by the value of the external resistor $(R_{DT})$ connected between DT pin and GNDI. The deadtime can be estimated as $t_{DT}$ (ns) $\approx 10 \times R_{DT}$ (k $\Omega$ ). If DT pin is pulled up to VDDI for disabling the deadtime and interlocking logic the OUTA and OUTB can be high simultaneously. Minimum deadtime will be observed between OUTA and OUTB when DT pin is left floating. |

|            |              |            | Allowed resistance between this pin and GNDI is in range of 5 to 500 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            |              |            | Maximum voltage on this pin is V <sub>DDI</sub> .  Corresponding waveforms are on Figure 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AND        | 7            | lanut      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ANB        | 7            | Input      | A high signal on ANB (A-and-B) pin enables OUTA and OUTB as complementary outputs from one PWM input signal on INA. INB must be connected to INA when ANB is high. ANB should be kept low when OUTA and OUTB are controlled individually by INA, INB. It has an equivalent pull-down resistor of 100 k to ensure that ANB pin will not be floating. Leaving this pin floating for proper security features is not recommended.                                                                                                                |

|            |              |            | The input logic levels scale with $V_{DDI}$ up to $V_{DDI}$ = 5 V. With $V_{DDI}$ above 5 V the input logic levels stay the same as for $V_{DDI}$ = 5 V. Maximum voltage on this pin is $V_{DDI}$ .                                                                                                                                                                                                                                                                                                                                           |

| GNDB       | 9            | Power      | Ground for channel B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUTB       | 10           | Output     | Output of channel B on the high voltage side. It has galvanic isolation from low voltage side and from channel A. OUTB provides the appropriate drive voltage and source/sink current to the IGBT/MOSFET gate. OUTB is actively pulled low during startup, when DIS is high and under UVLOB, UVLOI condition. INB must be connected to INA when ANB is high.                                                                                                                                                                                  |

|            |              |            | There is interlocking logic that prevents OUTA and OUTB cross conduction when DT pin is not connected to $V_{DDI}$ .                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_{DDB}$  | 11           | Power      | High voltage side power supply for channel B. A good quality bypassing capacitor is required from this pin to GNDB and should be placed close to the pins for best results.                                                                                                                                                                                                                                                                                                                                                                   |

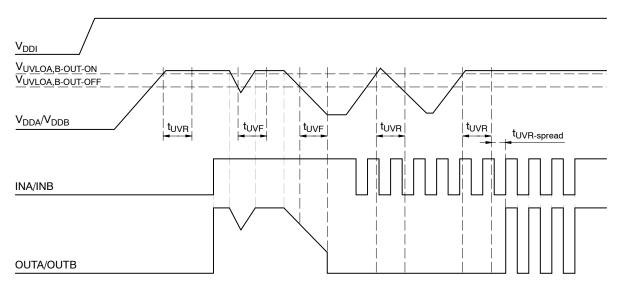

|            |              |            | The under voltage lockout (UVLOB) circuit enables the device to operate at power on when a typical supply voltage higher than V <sub>UVLOB-OUT-ON</sub> is present.                                                                                                                                                                                                                                                                                                                                                                           |

| NC         | 10 10        |            | Please see Figure 9 and 10 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC<br>GNDA | 12, 13<br>14 | -<br>Power | Not connected internally.  Ground for channel A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |              | _          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUTA       | 15           | Output     | Output of channel A on the high voltage side. It has galvanic isolation from low voltage side and from channel B. OUTA provides the appropriate drive voltage and source/sink current to the IGBT/MOSFET gate. OUTA is actively pulled low during startup, when DIS is high and under UVLOA, UVLOI condition.  There is interlocking logic that prevents OUTA and OUTB cross conduction when DT pin is not                                                                                                                                    |

|            |              |            | connected to V <sub>DDI</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 1. FUNCTION DESCRIPTION (continued)

| Pin Name           | No. | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\mathrm{DDA}}$ | 16  | Power | High voltage side power supply for channel A. A good quality bypassing capacitor is required from this pin to GNDA and should be placed close to the pins for best results.  The under voltage lockout (UVLOA) circuit enables the device to operate at power on when a typical supply voltage higher than V <sub>UVLOA-OUT-ON</sub> is present.  Please see Figure 9 and 10 for more details. |

#### **Table 2. SAFETY AND INSULATION RATINGS**

| Symbol                 | Parameter                                                                                                                                  |                         | Min          | Тур       | Max    | Unit            |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|-----------|--------|-----------------|

|                        | Installation Classifications per DIN VDE 0110/1.89                                                                                         | < 150 V <sub>RMS</sub>  | -            | I–IV      | _      |                 |

|                        | Table 1 Rated Mains Voltage                                                                                                                | < 300 V <sub>RMS</sub>  | -            | I–IV      | _      |                 |

|                        |                                                                                                                                            | < 450 V <sub>RMS</sub>  | -            | I–IV      | -      |                 |

|                        |                                                                                                                                            | < 600 V <sub>RMS</sub>  | -            | I–IV      | -      |                 |

|                        |                                                                                                                                            | < 1000 V <sub>RMS</sub> | -            | I–III     | _      |                 |

| CTI                    | Comparative Tracking Index (DIN IEC 112/VDE 0303                                                                                           | 3 Part 1)               | 600          | -         | _      |                 |

|                        | Climatic Classification                                                                                                                    |                         | -            | 40/100/21 | _      |                 |

|                        | Pollution Degree (DIN VDE 0110/1.89)                                                                                                       |                         | -            | 2         | _      |                 |

| $V_{PR}$               | Input–to–Output Test Voltage, Method b, $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1$ s, Partial Discharge < 5 pC |                         | 2250         | -         | -      | V <sub>PK</sub> |

| V <sub>IORM</sub>      | Maximum Working Insulation Voltage                                                                                                         |                         | 1200         | -         | _      | $V_{PK}$        |

| $V_{IOTM}$             | Highest Allowable Over Voltage<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                       |                         | 4200<br>8400 | -<br>-    | -<br>- | V <sub>PK</sub> |

| E <sub>CR</sub>        | External Creepage<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                                    |                         | 4.0<br>8.0   | -<br>-    | -<br>- | mm              |

| E <sub>CL</sub>        | External Clearance<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                                   |                         | 4.0<br>8.0   |           | -<br>- | mm              |

| DTI                    | Insulation Thickness<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                                 |                         | 8.65<br>17.3 | -<br>-    | -<br>- | μm              |

| T <sub>Case</sub>      | Safety Limit Values – Maximum Values in Failure; Case Temperature                                                                          |                         | 150          | -         | -      | °C              |

| P <sub>S,INPUT</sub>   | Safety Limit Values – Maximum Values in Failure; Input Power                                                                               |                         | 264          | -         | -      | mW              |

| P <sub>S,ОUТР</sub> UТ | Safety Limit Values – Maximum Values in Failure; Output Power SOIC–16 (NCx 57255, NCx 57256) SOIC–16WB (NCx 57252, NCx 57253)              |                         | 796<br>1136  | -<br>-    | -<br>- | mW              |

| R <sub>IO</sub>        | Insulation Resistance at TS, V <sub>IO</sub> = 500 V                                                                                       |                         | 109          | _         | _      | Ω               |

Table 3. ABSOLUTE MAXIMUM RATINGS (Note 1) Over operating free-air temperature range unless otherwise noted

| Symbol                 | Parameter                                                                                                                                                                                    | Minimum        | Maximum                | Unit |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|------|

| V <sub>DDI</sub> -GNDI | Supply voltage, low voltage side                                                                                                                                                             | -0.3           | 22                     | V    |

| V <sub>DDA</sub> -GNDA | Supply voltage, high voltage side, channel A                                                                                                                                                 | -0.3           | 36                     | V    |

| V <sub>DDB</sub> -GNDB | Supply voltage, high voltage side, channel B                                                                                                                                                 | -0.3           | 36                     | V    |

| V <sub>OUTA</sub>      | Gate driver output voltage, channel A                                                                                                                                                        | GNDA - 0.3     | V <sub>DDA</sub> + 0.3 | V    |

| V <sub>OUTB</sub>      | Gate driver output voltage, channel B                                                                                                                                                        | GNDB - 0.3     | V <sub>DDB</sub> + 0.3 | V    |

| I <sub>PK-SRC</sub>    | Gate-driver output sourcing current (maximum pulse width = 10 μs, minimum period = 5 ms, V <sub>DDA</sub> - GNDA = V <sub>DDB</sub> - GNDB = 15 V) (NCx57252, NCx57253) (NCx57255, NCx57256) | -              | 6.5<br>3.5             | A    |

| I <sub>PK-SNK</sub>    | Gate-driver output sinking current (maximum pulse width = 10 μs, minimum period = 5 ms, V <sub>DDA</sub> - GNDA = V <sub>DDB</sub> - GNDB = 15 V) (NCx57252, NCx57253) (NCx57255, NCx57256)  | =              | 6.5<br>3.5             | A    |

| t <sub>CLP</sub>       | Maximum Short Circuit Clamping Time (IOUTA_CLAMP = IOUTB_CLAMP = 500 mA)                                                                                                                     | -              | 10                     | μs   |

| V <sub>LIM</sub> -GNDI | Voltage at INA, INB, DIS, DT, ANB                                                                                                                                                            | -0.3           | V <sub>DDI</sub> + 0.3 | V    |

| PD                     | Power Dissipation (Note 3)<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                                                                             | -              | 1400<br>1060           | mW   |

| $V_{IOWM}$             | Input to Output Isolation Voltage<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)                                                                                      | -2500<br>-5000 | 2500<br>5000           | V    |

| T <sub>J</sub> (max)   | Maximum Junction Temperature                                                                                                                                                                 | -40            | 150                    | °C   |

| T <sub>STG</sub>       | Storage Temperature Range                                                                                                                                                                    | -65            | 150                    | °C   |

| ESDHBM                 | ESD Capability, Human Body Model (Note 4)                                                                                                                                                    | -              | ±4                     | kV   |

| ESDCDM                 | ESD Capability, Charged Device Model (Note 4)                                                                                                                                                | -              | ±2                     | kV   |

| MSL                    | Moisture Sensitivity Level                                                                                                                                                                   | -              | 1                      | _    |

| T <sub>SLD</sub>       | Lead Temperature Soldering Reflow, Pb-Free Versions (Note 5)                                                                                                                                 | -              | 260                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. The minimum value is verified by characterization with a single pulse of 100 mA for 100  $\mu$ s.

- 3. The value is estimated for ambient temperature 25°C and junction temperature 150°C, 650 mm², 1 oz copper, 2 surface layers and 2 internal power plane layers. Power dissipation is affected by the PCB design and ambient temperature.

- 4. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114).

- ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101)

- Latchup Current Maximum Rating: ≤ 100 mA per JEDEC standard: JESD78, 25°C.

- 5. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **Table 4. THERMAL CHARACTERISTICS**

| Parameter                                                                  | Conditions                                                                               | Symbol          | Value | Unit |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|-------|------|

| Thermal Resistance, Junction – to – Air SOIC – 16 (NCx 57255, NCx 57256)   | 100 mm <sup>2</sup> , 2 oz Copper, 1 Surface Layer                                       | $R_{\theta JA}$ | 164   | °C/W |

| 3010-10 (NOX 37233, NOX 37230)                                             | 100 mm <sup>2</sup> , 2 oz Copper, 2 Surface Layers<br>and 2 Internal Power Plane Layers |                 | 118   |      |

| Thermal Resistance, Junction – to – Air SOIC – 16WB (NCx 57252, NCx 57253) | 100 mm <sup>2</sup> , 2 oz Copper, 1 Surface Layer                                       | $R_{\theta JA}$ | 81    | °C/W |

| 3010-10WB (NOX 37232, NOX 37233)                                           | 100 mm <sup>2</sup> , 2 oz Copper, 2 Surface Layers and 2 Internal Power Plane Layers    |                 | 57    |      |

Table 5. RECOMMENDED OPERATING RANGES (Note 6)

| Symbol                 | Parameter                                     | Minimum | Maximum   | Unit  |

|------------------------|-----------------------------------------------|---------|-----------|-------|

| V <sub>DDI</sub> -GNDI | Supply voltage, low voltage side              | UVLOI   | 20        | V     |

| V <sub>DDA</sub> -GNDA | Supply voltage, high voltage side, channel A  | UVLOA   | 32        | V     |

| V <sub>DDB</sub> -GNDB | Supply voltage, high voltage side, channel B  | UVLOB   | 32        | V     |

| V <sub>IN</sub>        | Logic Input Voltage at INA, INB, DIS, DT, ANB | GNDI    | $V_{DDI}$ | V     |

| dV <sub>ISO</sub> /dt  | Common Mode Transient Immunity (CMTI)         | 100     |           | kV/μs |

| T <sub>A</sub>         | Ambient Temperature                           | -40     | 125       | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Table 6. ISOLATION CHARACTERISTICS**

| Symbol                    | Parameter                          | Conditions                                                                                                                                                                                                                                                                          | Min              | Тур    | Max    | Unit             |

|---------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|--------|------------------|

| VISO, IINPUT<br>TO OUTPUT | Input-Output Isolation<br>Voltage  | $\begin{array}{l} T_{A} = 25^{\circ}\text{C}, \ \text{Relative Humidity} < 50\%, \\ t = 1.0 \ \text{minute}, \ l_{I-O} \ 10 \ \text{A}, \ 50 \ \text{Hz} \\ \text{(Notes 7, 8, 9)} \\ \text{SOIC-16 (NCx 57255, NCx 57256)} \\ \text{SOIC-16WB (NCx 57252, NCx 57253)} \end{array}$ | 2500<br>5000     | -<br>- | -<br>- | V <sub>RMS</sub> |

| VISO, OUTPUT<br>TO OUTPUT | Output-Output Isolation<br>Voltage | $\begin{array}{l} T_{A} = 25^{\circ}\text{C}, \ \text{Relative Humidity} < 50\%, \\ t = 1.0 \ \text{minute}, \ I_{I-O} \ 10 \ \text{A}, \ 50 \ \text{Hz} \\ \text{(Notes 7, 8, 9)} \\ \text{SOIC-16 (NCx 57255, NCx 57256)} \\ \text{SOIC-16WB (NCx 57252, NCx 57253)} \end{array}$ | 1500<br>1500     | -<br>- | -<br>- | V <sub>RMS</sub> |

| R <sub>ISO</sub>          | Isolation Resistance               | V <sub>I-O</sub> = 500 V (Note 7)                                                                                                                                                                                                                                                   | 10 <sup>11</sup> |        |        | Ω                |

<sup>7.</sup> Device is considered a two-terminal device: pins 1 to 8 are shorted together and pins 9 to 16 are shorted together.

**Table 7. ELECTRICAL CHARACTERISTICS**  $V_{DDI} = 5V$ ,  $V_{DDA} = V_{DDB} = 15 V$

For typical values  $T_A = 25^{\circ}C$ , for min/max values,  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.

| Symbol                      | Parameter                                                                               | Test Conditions                                     | Min  | Тур  | Max  | Unit |

|-----------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| VOLTAGE SUPPLY              |                                                                                         |                                                     |      |      |      |      |

| V <sub>UVLOI-OUT-ON</sub>   | V <sub>DDI</sub> Supply Under Voltage Output Enabled                                    |                                                     |      |      | 3.1  | V    |

| V <sub>UVLOI</sub> -OUT-OFF | V <sub>DDI</sub> Supply Under Voltage Output Disabled                                   |                                                     | 2.4  |      |      | V    |

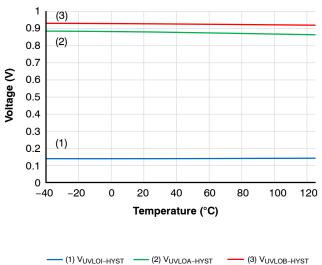

| V <sub>UVLOI-HYST</sub>     | V <sub>DDI</sub> Supply Voltage Output<br>Enabled/Disabled Hysteresis                   |                                                     | 0.1  |      |      | V    |

| V <sub>UVLOA-OUT-ON</sub>   | V <sub>DDA</sub> /V <sub>DDB</sub> Supply Under Voltage                                 | NCx57252/NCx57255                                   | 12.4 | 12.9 | 13.4 | V    |

| V <sub>UVLOB-OUT-ON</sub>   | Output Enabled                                                                          | NCx57253/NCx57256                                   | 8.7  | 9    | 9.3  | V    |

| V <sub>UVLOA-OUT-OFF</sub>  | V <sub>DDA</sub> /V <sub>DDB</sub> Supply Under Voltage                                 | NCx57252/NCx57255                                   | 11.5 | 12   | 12.5 | V    |

| V <sub>UVLOB-OUT-OFF</sub>  | Output Disabled                                                                         | NCx57253/NCx57256                                   | 7.7  | 8    | 8.3  | V    |

| V <sub>UVLOA/B</sub> -HYST  | V <sub>DDA</sub> /V <sub>DDB</sub> Supply Voltage Output<br>Enabled/Disabled Hysteresis |                                                     | 0.8  | 1.0  |      | V    |

| I <sub>QDDI-0</sub>         | Low Voltage Side Quiescent Current                                                      | V <sub>INA</sub> = V <sub>INB</sub> = 0 V           |      |      | 2    | mA   |

| I <sub>QDDI-50</sub>        | Low Voltage Side Operating Current at 50% Duty Cycle                                    | INA PWM, INB Low (or INA Low, INB PWM), f = 200 kHz |      |      | 4    | mA   |

| I <sub>QDDI-100</sub>       | Low Voltage Side Operating Current at 100% Duty Cycle                                   | INA or INB High                                     |      |      | 6    | mA   |

<sup>6.</sup> Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

<sup>5,000</sup> V<sub>RMS</sub> for 1-minute duration is equivalent to 6,000 V<sub>RMS</sub> for 1-second duration.

2,500 VRMS for 1-minute duration is equivalent to 3,000 VRMS for 1-second duration.

The input-output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input-output continuous voltage

rating. For the continuous working voltage rating, refer to equipment-level safety specification or DIN VDE V 0884-11 Safety and Insulation

Ratings Table.

**Table 7. ELECTRICAL CHARACTERISTICS** (continued)  $V_{DDI} = 5V$ ,  $V_{DDA} = V_{DDB} = 15 V$ For typical values  $T_A = 25^{\circ}C$ , for min/max values,  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.

| Symbol                                                                                             | Parameter                                                                                                             | Test Conditions                                                                               | Min                       | Тур                        | Max                     | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|----------------------------|-------------------------|------|

| VOLTAGE SUPPLY                                                                                     |                                                                                                                       |                                                                                               |                           |                            |                         |      |

| I <sub>QDDA-0</sub> , I <sub>QDDB-0</sub>                                                          | High Voltage Side Quiescent<br>Current                                                                                | V <sub>INA</sub> = V <sub>INB</sub> = 0 V,<br>Current per Channel                             |                           |                            | 2                       | mA   |

| I <sub>QDDA-50</sub> ,<br>I <sub>QDDB-50</sub>                                                     | High Voltage Side Operating<br>Current at 50% Duty Cycle                                                              | Current per Channel,<br>f = 200 kHz, C <sub>G</sub> = 1 nF                                    |                           |                            | 2                       | mA   |

| I <sub>QDDA-100</sub> ,<br>I <sub>QDDB-100</sub>                                                   | High Voltage Side Operating<br>Current at 100% Duty Cycle                                                             | Current per Channel                                                                           |                           |                            | 2                       | mA   |

| LOGIC INPUT                                                                                        |                                                                                                                       |                                                                                               |                           |                            |                         |      |

| V <sub>INAL</sub> , V <sub>INBL</sub> ,<br>V <sub>DISL</sub> , V <sub>ANBL</sub>                   | Low Level Input Voltage                                                                                               | Level scale for $V_{DDI}$ = 3.3 to 5 V for $V_{DDI}$ > 5 V is the same as for $V_{DDI}$ = 5 V |                           |                            | $^{0.3	imes}_{V_{DDI}}$ | V    |

| V <sub>INAH</sub> , V <sub>INBH</sub> ,<br>V <sub>DISH</sub> , V <sub>ANBH</sub>                   | High Level Input Voltage                                                                                              | Level scale for $V_{DDI}$ = 3.3 to 5 V for $V_{DDI}$ > 5 V is the same as for $V_{DDI}$ = 5 V | 0.7 ×<br>V <sub>DDI</sub> |                            |                         | V    |

| V <sub>INA-HYS</sub> ,<br>V <sub>INB-HYS</sub> ,<br>V <sub>DIS-HYS</sub> ,<br>V <sub>ANB-HYS</sub> | Input Hysteresis                                                                                                      | Level scale for $V_{DDI}$ = 3.3 to 5 V for $V_{DDI}$ > 5 V is the same as for $V_{DDI}$ = 5 V |                           | 0.15 ×<br>V <sub>DDI</sub> |                         | V    |

| V <sub>INAN</sub> , V <sub>INBN</sub> ,<br>V <sub>DISN</sub> , V <sub>ANBN</sub><br>(Note 10)      | Negative Input Transient                                                                                              | 50 ns                                                                                         | -5                        |                            |                         | V    |

| I <sub>INAH</sub> , I <sub>INBH</sub> ,<br>I <sub>DISH</sub> , I <sub>ANBH</sub>                   | Logic "1" Input Bias Current                                                                                          | $V_{INA} = V_{INB} = V_{DIS} = V_{ANB} = V_{DDI} = 3.3 \text{ V}$                             |                           | 50                         |                         | μΑ   |

| I <sub>INAH</sub> , I <sub>INBH</sub> ,<br>I <sub>DISH</sub> , I <sub>ANBH</sub>                   | Logic "1" Input Bias Current                                                                                          | $V_{INA} = V_{INB} = V_{DIS} = V_{ANB} = V_{DDI} = 20 \text{ V}$                              |                           | 50                         |                         | μΑ   |

| I <sub>INAL</sub> , I <sub>INBL</sub> ,<br>I <sub>DISL</sub> , I <sub>ANBL</sub>                   | Logic "0" Input Bias Current                                                                                          | $V_{INA} = V_{INB} = V_{DIS} = V_{ANB} = 0 V$                                                 |                           | 1                          |                         | μΑ   |

| DRIVER OUTPUT                                                                                      |                                                                                                                       |                                                                                               |                           | •                          |                         |      |

| V <sub>OUTAL1</sub> , V <sub>OUTBL1</sub><br>V <sub>OUTAL2</sub> , V <sub>OUTBL2</sub>             | Output Low State                                                                                                      | $I_{SINK}$ = 200 mA, $T_A$ = 25°C $I_{SINK}$ = 200 mA, $T_A$ = -40°C to 125°C                 |                           | 0.1                        | 0.22<br>0.5             | V    |

| V <sub>OUTAH1</sub> , V <sub>OUTBH1</sub><br>V <sub>OUTAH2</sub> , V <sub>OUTBH2</sub>             | Output High State                                                                                                     | $I_{SRC}$ = 200 mA, $T_{A}$ = 25°C<br>$I_{SRC}$ = 200 mA, $T_{A}$ = -40°C to 125°C            | 14.7<br>14.2              | 14.8                       |                         | V    |

| I <sub>PK-SNK1</sub>                                                                               | Peak Driver Current, Sink (Note 10)<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)             |                                                                                               |                           | 3.5<br>6.5                 |                         | Α    |

| I <sub>PK</sub> -SNK2                                                                              | Peak Miller Plateau Current, Sink<br>(Note 10)<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)  | V <sub>OUTA</sub> = V <sub>OUTB</sub> = 6 V<br>(near IGBT Miller Plateau)                     |                           | 3<br>6                     |                         | Α    |

| I <sub>PK</sub> -SRC1                                                                              | Peak Driver Current, Source (Note 10)<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253)           |                                                                                               |                           | 3.5<br>6.5                 |                         | Α    |

| I <sub>PK-SRC2</sub>                                                                               | Peak Miller Plateau Current, Source<br>(Note 7)<br>SOIC-16 (NCx 57255, NCx 57256)<br>SOIC-16WB (NCx 57252, NCx 57253) | V <sub>OUTA</sub> = V <sub>OUTB</sub> = 9 V<br>(near IGBT Miller Plateau)                     |                           | 3<br>6                     |                         | Α    |

| IGBT SHORT CIRC                                                                                    | UIT CLAMPING                                                                                                          |                                                                                               |                           |                            |                         |      |

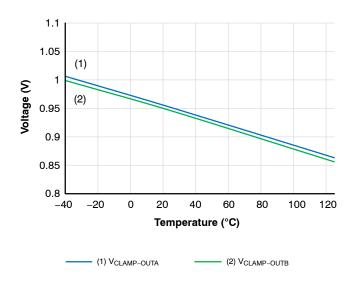

| V <sub>CLAMP</sub> -OUTA,<br>V <sub>CLAMP</sub> -OUTB                                              | Clamping Voltage<br>(V <sub>CLAMP-OUTA</sub> - V <sub>DDA</sub> ),<br>(V <sub>CLAMP-OUTB</sub> - V <sub>DDB</sub> )   | $I_{OUTA} = I_{OUTB} = 500 \text{ mA}$<br>(pulse test, $t_{CLPmax} = 10 \mu\text{s}$ )        |                           | 0.4                        | 0.6                     | V    |

Table 7. ELECTRICAL CHARACTERISTICS (continued)  $V_{DDI} = 5V$ ,  $V_{DDA} = V_{DDB} = 15 V$

For typical values T<sub>A</sub> = 25°C, for min/max values, T<sub>A</sub> is the operating ambient temperature range that applies, unless otherwise noted.

| Symbol                   | Parameter                                                                                   | Test Conditions                                                                      | Min | Тур | Max | Unit |

|--------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| YNAMIC CHARA             | ACTERISTIC                                                                                  | •                                                                                    |     |     | 1   |      |

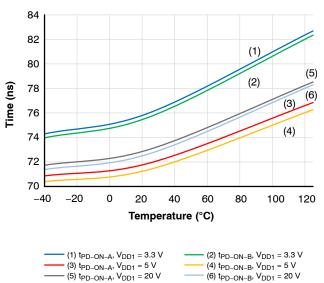

| t <sub>PD-ON-A</sub>     | OUTA High Propagation Delay                                                                 | C <sub>LOAD</sub> = 10 nF, V <sub>INAH</sub> to 10% of Output Change for PW > 150 ns | 40  | 60  | 80  | ns   |

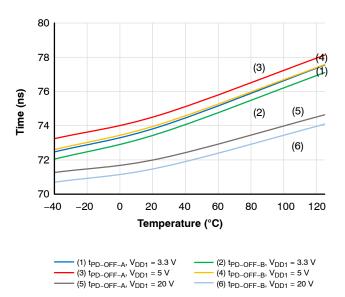

| t <sub>PD-OFF-A</sub>    | OUTA Low Propagation Delay                                                                  | C <sub>LOAD</sub> = 10 nF, V <sub>INAL</sub> to 90% of Output Change for PW > 150 ns | 40  | 60  | 80  | ns   |

| t <sub>DISTORT-A</sub>   | Propagation Delay Distortion<br>(Channel A) (t <sub>PD-ON-A</sub> - t <sub>PD-OFF-A</sub> ) | PW >150 ns                                                                           | -20 | 0   | 20  | ns   |

| t <sub>PD-ON-B</sub>     | OUTB High Propagation Delay                                                                 | C <sub>LOAD</sub> = 10 nF, V <sub>INBH</sub> to 10% of Output Change for PW > 150 ns | 40  | 60  | 80  | ns   |

| t <sub>PD-OFF-B</sub>    | OUTB Low Propagation Delay                                                                  | C <sub>LOAD</sub> = 10 nF, V <sub>INBL</sub> to 90% of Output Change for PW > 150 ns | 40  | 60  | 80  | ns   |

| t <sub>DISTORT-B</sub>   | Propagation Delay Distortion<br>(Channel B) (tpD-ON-B - tpD-OFF-B)                          | PW >150 ns                                                                           | -20 | 0   | 20  | ns   |

| t <sub>DISTORT-ON</sub>  | Rising Edge Propagation Delay Distortion (t <sub>PD-ON-A</sub> - t <sub>PD-ON-B</sub> )     | PW >150 ns                                                                           | -20 | 0   | 20  | ns   |

| t <sub>DISTORT-OFF</sub> | Falling Edge Propagation Delay Distortion (tpD-OFF-A - tpD-OFF-B)                           | PW >150 ns                                                                           | -20 | 0   | 20  | ns   |

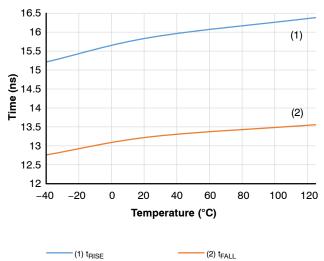

| t <sub>RISE</sub>        | Rise Time for Both Channel A and B                                                          | C <sub>LOAD</sub> = 1 nF, 10% to 90% of Output Change                                |     | 12  |     | ns   |

| t <sub>FALL</sub>        | Fall Time for Both Channel A and B                                                          | C <sub>LOAD</sub> = 1 nF, 90% to 10% of Output Change                                |     | 10  |     | ns   |

| t <sub>DT</sub>          | Deadtime between channels                                                                   | DT pin Float                                                                         |     | <20 |     | ns   |

|                          |                                                                                             | $R_{DT}$ = 500 k $\Omega$                                                            |     | 5   |     | μs   |

|                          |                                                                                             | $R_{DT}$ = 20 k $\Omega$                                                             |     | 200 |     | ns   |

| t <sub>DIS</sub>         | Disable Delay                                                                               |                                                                                      |     | 60  |     | ns   |

| t <sub>MIN1</sub>        | Input Pulse Width for no output                                                             | Positive pulse (L–H–L), T <sub>A</sub> = 25°C                                        |     |     | 10  | ns   |

|                          |                                                                                             | Negative pulse (H-L-H), T <sub>A</sub> = 25°C                                        |     |     | 10  | ns   |

| t <sub>MIN2</sub>        | Input Pulse Width for guaranteed                                                            | Positive pulse (L-H-L), T <sub>A</sub> = 25°C                                        | 40  |     |     | ns   |

|                          | output                                                                                      | Negative pulse (H–L–H), T <sub>A</sub> = 25°C                                        | 40  |     |     | ns   |

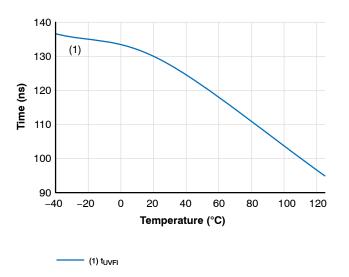

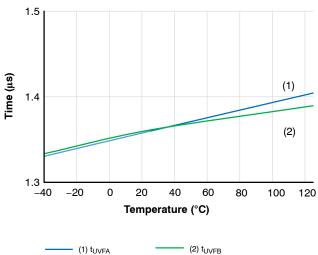

| t <sub>UVF</sub>         | UVLOI/UVLOA/UVLOB Fall Delay                                                                | (Note 10)                                                                            |     | 1.5 |     | μs   |

| t <sub>UVR</sub>         | UVLOI/UVLOA/UVLOB Rise Delay                                                                | (Note 10)                                                                            | 10  | 20  |     | μS   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

10. Values based on design and/or characterization.

#### **Modes of Operation**

The NCx5725y can operate in 3 distinct modes:

- 1. The low–side, high–side half–bridge driver with *two* inputs and programmable dead–time.

- 2. The low-side, high-side half-bridge driver with *one* input and programmable dead-time.

- 3. The two independent (potentially overlapping) channels with two inputs.

1st mode – half-bridge driver with two inputs and adjustable dead-time is for applications where you have high-side and low-side PWM available. The driver provides interlock function to prevent activation of high-side and low-side outputs at the same time. In addition

the driver generates dead-time which is adjustable by DT pin.

The typical application schematics are on Figure 2 and 3.

- ANB pin has to be connected to GNDI in this mode.

- The dead-time is set by resistor R<sub>DT</sub> connected between DT pin and GNDI. Adjusting dead-time is described in the section Dead-time (DT).

2<sup>nd</sup> mode – half-bridge driver with one input and adjustable dead-time is very similar to 1<sup>st</sup> mode but just high-side PWM is needed. The low-side PWM is internally generated by the driver. Interlock and dead-time generator works the same as in 1<sup>st</sup> mode.

<sup>11.</sup> PW = Pulse Width

- Both INA and INB have to be connected together.

- ANB pin has to be connected to V<sub>DDI</sub>. This enables the internal complementary low-side PWM generator.

- The dead-time is set by resistor R<sub>DT</sub> connected between DT pin and GNDI. Adjusting dead-time is described in the section Dead-time (DT).

3<sup>rd</sup> mode – driver with two independent channels and two inputs is different from previous two modes because it allows for completely independent and even overlapping PWMs to drive the outputs individually.

- The ANB pin has to be connected to GNDI.

- DT pin has to be connected to V<sub>DDI</sub>. This disables the interlock function and dead-time generator and allows the overlapping PWMs. So the channel A and B can be driven completely independently.

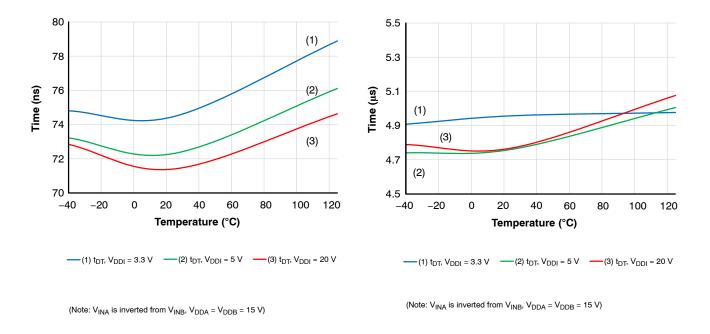

#### Dead-Time (DT)

The dead-time pin is controlling the integrated interlock and dead-time generator.

- If DT pin is connected to V<sub>DDI</sub> the interlock and dead-time generator are disabled. The channels A and B are completely independent.

- If DT pin is floating the interlock is enabled but dead-time generator is disabled. There is a minimal dead-time shorter than 20 ns.

- If there is a resistor R<sub>DT</sub> connected between the DT pin and GNDI the interlock and dead-time generator are both

- enabled. The dead-time can be adjusted in range from 200 ns  $(R_{DT}\approx 20~k\Omega)$  to 5  $\mu s~(R_{DT}\approx 500~k\Omega)$ . Dead-time can be estimated by the equation  $t_{DT}$  (ns)  $\approx 10~x~R_{DT}$  (k $\Omega$ ). With high  $R_{DT}$  values the potential noise pick-up on high impedance of  $R_{DT}$  should be considered.  $R_{DT}$  should be as close to driver pins as possible and the loop should be minimized.

- If  $R_{DT}$  is below 20 k $\Omega$  the DT is not closely following the equation but dead-times lower than 200 ns could be achieved. The lowest allowed value of  $R_{DT}$  = 5 k $\Omega$  which reduces the dead-time to about 70 ns.

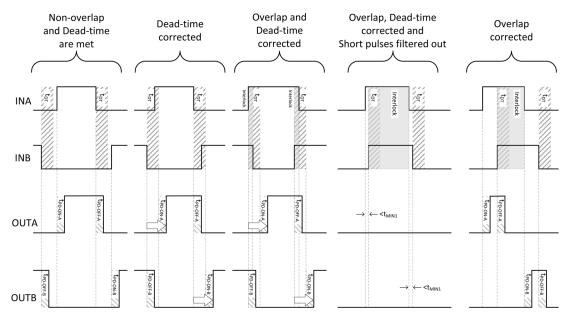

The Figures 2 and 3 illustrate the behavior of the NCx5725y in 1<sup>st</sup> mode (high-side, low-side half-bridge driver with two inputs). The outputs for various input PWM combinations are shown in Figure 5.

The dead-time is a time from low-side output going low to high-side output going high or from high-side output going low to low side output going high. The overlap is a situation where both signals are high at the same time. Overlap causes cross conduction in the half-bridge and must be avoided.

In the "Non-overlap and Dead-time are met" column in Fig. 5, the channel A PWM, INA (high-side), and channel B PWM, INB (low-side), are not overlapping and have sufficient dead-time. Therefore, the driver does not apply corrections to the signals and passes them as they are to their respective output.

Figure 5. Deadtime, Interlock and Output Minimum Pulse Width

In the "Dead-time corrected" column, the high-side and low-side signals are not overlapping but the dead-time value is less than the value set through the DT pin. Consequently, the driver increases the dead-time value to the value set by the DT pin.

In the "Overlap and Dead-time corrected" column, the high-side and low-side input signals are high at the same time (overlapping). This condition could cause cross-conduction in the half-bridge. Therefore, the driver's interlock function trims signal OUTB which is going low

when INA goes high, and not when INB goes low. The driver also inserts the dead-time set through DT pin, thus the output pulses are not overlapping and cross-conduction in the half-bridge is avoided.

In the "Overlap, Dead-time corrected and Short pulses filtered out" column, the high-side and low side signals are overlapping and could cause cross-conduction in the half-bridge. Therefore, the driver's interlock function trims the output signals and a short spike remains on each output signal. If the spike is shorter than tMIN1 (Minimum pulse width filtering time), it will be suppressed and no output is generated.

In the "Overlap corrected" column the dead-time is met but the signals are overlapping so just the non-overlapping parts pass to the output.

#### Inputs INA, INB, DIS, ANB

Unused inputs should be tied to GNDI.

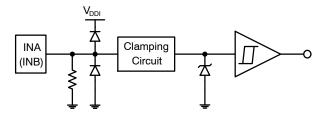

#### Input Voltage Levels

The NCx5725y has a two modes for high and low levels on all input pins:

- 1. For  $V_{DDI}$  from 3.3 to 5 V the high and low input levels are scaling with the  $V_{DDI}$  as stated in the Electrical characteristics table. Low input level is  $0.3 \times V_{DDI}$ , high input level is  $0.7 \times V_{DDI}$ .

- 2. For  $V_{DDI}$  above 5 V the high and low input levels clamp at the same value as for  $V_{DDI} = 5$  V. That means the low input level is  $0.3 \times 5 = 1.5$  V and the high input level is  $0.7 \times 5 = 3.5$  V.

Figure 6. Input Pin Structure

#### **Edge Triggered Inputs**

The INA, INB and DIS inputs are activated by a signal edge (edge triggered), not with signal level. This means that after power cycling the driver, a rising edge has to occur on INA, INB for OUTA and OUTB to go high, respectively. The same conditions apply if the output signals are disabled through the DIS pin. Therefore, after DIS signal goes low, a rising edge has to occur on INA, INB for OUTA and OUTB to go high, respectively.

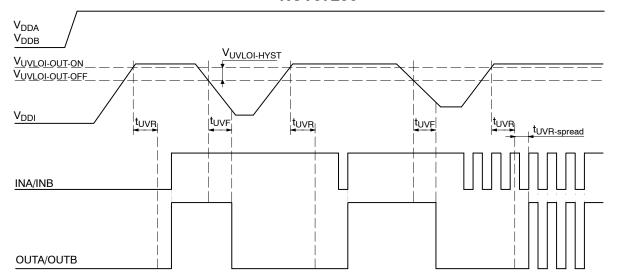

#### Under Voltage Lockout UVLOI, UVLOA, UVLOB

UVLOA and UVLOB ensures correct driving of the gates of the IGBTs (NCx57252, NCx57255) or MOSFETs (NCx57253, NCx57256). Driving the IGBT/MOSETS with low gate voltage causes it to switch outside the saturation region (in the linear region) which significantly increases the power losses and there is a danger of damage.

UVLOI ensures correct transmission of the signals from the primary side to the secondary side of the driver.

NCx5725y is equipped by edge triggered inputs in order to prevent output pulse trimming. Therefore, after returning from safe state to active state, a rising edge has to occur on INA, INB in order to set OUTA and OUTB high, respectively (see Figures 7, 8 and Figures 9, 10).

As a side effect of this feature is that the  $t_{UVR}$  time is always prolonged by a  $t_{UVR-spread}$ . The  $t_{UVR-spread}$  is the delay caused by the time before next rising edge of PWM signal comes.

Another note for the  $t_{UVR}$  is that it is valid if the  $V_{DD2}$  rises from just below  $V_{UVLO-OUT-OFF}$  to  $V_{UVLO-OUT-ON}$ . The cold–start time from  $V_{DDA(B)} = 0$  V to PWM at the output is  $t_{UVR}$  + startup time of the internal bias circuits. The whole time is about 20  $\mu$ s and the internal bias circuit startup time is about 10  $\mu$ s.

Figure 7. Output Ramp-up and Ramp-down Times during UVLOI

Figure 8. V<sub>DDI</sub> Glitch Filtering

Figure 9. Output Ramp-up and Ramp-down Times during UVLOA, UVLOB

Figure 10. V<sub>DDA</sub>/V<sub>DDB</sub> Glitch Filtering

#### **Power Supply**

Decoupling (VDDI, VDDA, VDDB)

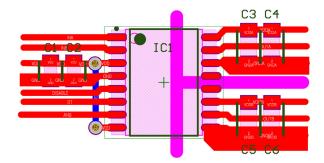

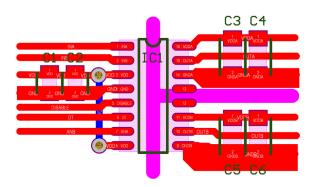

Suitable external power capacitors are required for reliable driving of IGBT/MOSFET gate with high current. Parallel combination of 100 nF + 4,7  $\mu$ F low ESR ceramic capacitors is optimal for a wide range of applications using IGBT/MOSFET. For reliable driving of IGBT modules (containing several parallel IGBT's) with a gate capacitance over 10 nF a higher decoupling capacity is required (typically 100 nF + 10  $\mu$ F). Capacitors should be as close as possible to the driver's power pins. The recommended layout is provided in the Figure 14.

#### Cooling Polygons on GNDA/GNDB

It is important to provide cooling polygons if driving IGBTs with higher gate capacitance values and using higher

switching frequencies. They have to be connected to GNDA and GNDB (See Figure 14 and 15).

#### **Output Current on GNDA/GNDB**

The NCx5725y has a high current, low-drop MOSFET output stage. It is capable of driving IGBTs with gate capacitance CG of up to 100 nF. For optimal IGBT/MOSFET driving a few conditions have to be met:

- Low inductance (wide and short) traces from OUTA (OUTB) to R<sub>G</sub> and to IGBT/MOSFET gate and from emitter (source) to GNDA (GNDB).

- Sufficient power rating of gate resistors RG.

- Reasonable combination of switching frequency f and gate capacitance C<sub>G</sub> of the IGBT/MOSFET.

- Good V<sub>DDA</sub> and V<sub>DDB</sub> decoupling (discussed above).

- Sufficient cooling pads (discussed above).

Low Inductance Traces

All the traces have to be as low inductance as possible due to the high current path from the driver output to IGBT/MOSFET gate. In practice that means wide tracks which are as short as possible. Tracks also have to be routed in order to not create big loops. The driving path (driver output, RG, IGBT/MOSFET gate) and return path (IGBT emitter/MOSFET source, GNDA or GNDB pin) have to be routed as a pair and not enclosing other components.

#### Disable (DIS) Pin

DIS (disable) pin allows to deactivate both outputs independently of inputs INA, INB, DT, ANB.

If the pin is set high both OUTA and OUTB are set low immediately.

If DIS is set low, the outputs OUTA/OUTB are restored after rising edge is detected on the INA/INB respectively.

It has an internal pull-down resistor of 125 k $\Omega$  to ensure that OUTA and OUTB react to INA, INB, DT and ANB in the absence of an external signal. External pull-down resistor 10–47 k $\Omega$  is recommended to prevent unwanted DIS activation by external interference. Direct connection to GNDI is recommended if the pin is not used.

Figure 11. Disable Function

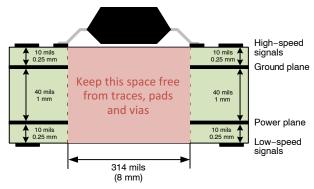

Figure 12. SOIC-16WB Recommended Layer Stack

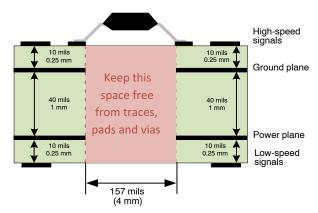

Figure 13. SOIC-16 Recommended Layer Stack

NOTE: Purple – Recommended isolation gap.

Figure 14. Recommended Layout (NCx57252, NCx57253)

Figure 15. Recommended Layout (NCx57255, NCx57256)

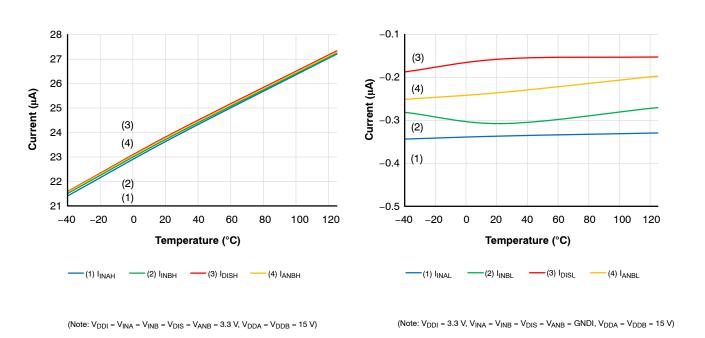

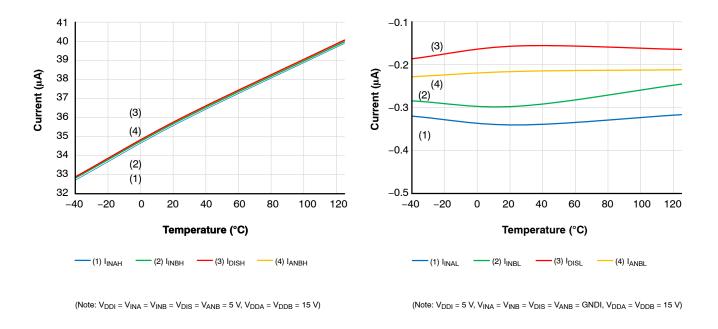

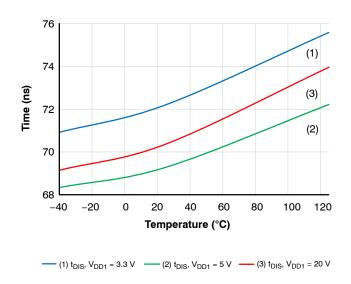

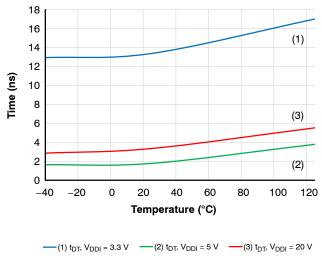

#### **TYPICAL CHARACTERISTICS**

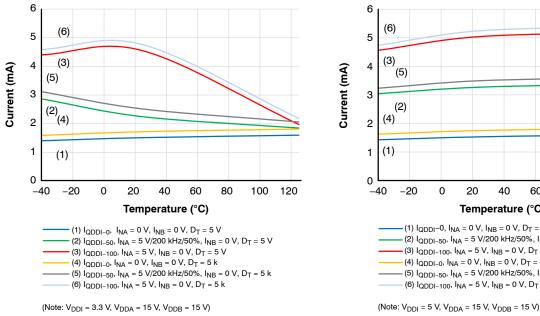

Figure 16. I<sub>QDDI</sub> Supply Current, V<sub>DDI</sub> = 3.3 V

Figure 18. I<sub>QDDI</sub> Supply Current, V<sub>DDI</sub> = 20 V

Figure 17. I<sub>QDDI</sub> Supply Current, V<sub>DDI</sub> = 5 V

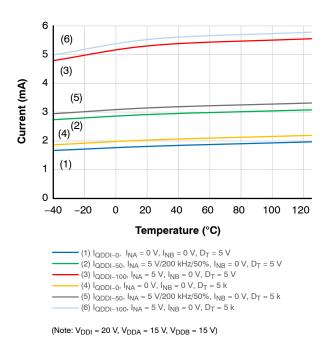

Figure 19. I<sub>QDDA</sub> Supply Current

#### **TYPICAL CHARACTERISTICS**

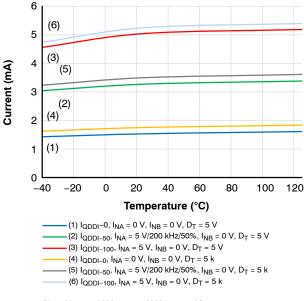

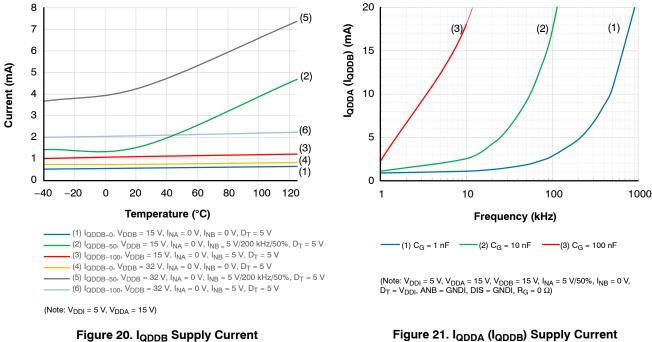

Figure 20. I<sub>QDDB</sub> Supply Current

Figure 22. Input Bias Current - Logic "1"

Figure 23. Input Bias Current - Logic "0"

vs. Switching Frequency

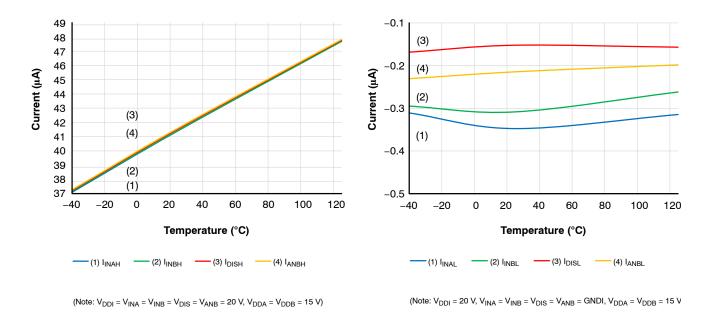

#### **TYPICAL CHARACTERISTICS**

Figure 24. Input Bias Current - Logic "1"

Figure 25. Input Bias Current - Logic "0"

Figure 26. Input Bias Current - Logic "1"

Figure 27. Input Bias Current - Logic "0"

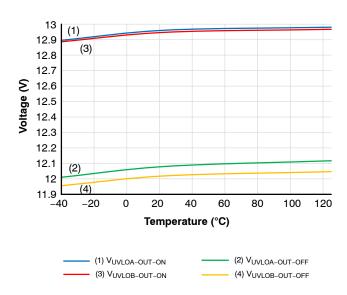

#### **TYPICAL CHARACTERISTICS**

9,1 (1) 8,9 (3) 8,7 Voltage (V) 8,5 8,3 (2)8,1 (4)7,9 -20 20 40 60 80 120 -40 0 100 Temperature (°C) (2) V<sub>UVLOA-OUT-OFF</sub> (1)  $V_{UVLOA-OUT-ON}$

(3) V<sub>UVLOB-OUT-ON</sub>

Figure 28. NCx57252 UVLOA and UVLOB Threshold Voltage

Figure 29. NCx57253 UVLOA and UVLOB

Threshold Voltage

(4) V<sub>UVLOB-OUT-OFF</sub>

Figure 30. UVLOI Threshold Voltage

Figure 31. UVLOx Enable/Disable Voltage Hysteresis

#### **TYPICAL CHARACTERISTICS**

Figure 32. UVLOI Fall Delay

Figure 33. UVLOA and UVLOB Fall Delay

Figure 34. IGBT Short Circuit Clamping Voltage

Figure 35. Propagation Delay Turn-on

#### **TYPICAL CHARACTERISTICS**

Figure 36. Propagation Delay Turn-off

Figure 37. Rise Time / Fall Time

(Note:  $V_{INA}$  is inverted from  $V_{INB}$ ,  $V_{DDA} = V_{DDB} = 15 V$ )

Figure 38. Disable Delay Time

Figure 39. Deadtime, DT pin FLOAT

#### **TYPICAL CHARACTERISTICS**

Figure 40. Deadtime, DT pin 5 k $\Omega$  to GNDI

Figure 41. Deadtime, DT pin 500  $k\Omega$  to GNDI

#### **ORDERING INFORMATION**

| Device         | Package                       | Shipping <sup>†</sup> |

|----------------|-------------------------------|-----------------------|

| NCD57252DWR2G  | SOIC-16 Wide Body (Pb-Free)   | 1,000 / Tape & Reel   |

| NCV57252DWR2G* | SOIC-16 Wide Body (Pb-Free)   | 1,000 / Tape & Reel   |

| NCD57253DWR2G  | SOIC-16 Wide Body (Pb-Free)   | 1,000 / Tape & Reel   |

| NCV57253DWR2G* | SOIC-16 Wide Body (Pb-Free)   | 1,000 / Tape & Reel   |

| NCD57255DR2G   | SOIC-16 Narrow body (Pb-Free) | 2,500 / Tape & Reel   |

| NCV57255DR2G*  | SOIC-16 Narrow body (Pb-Free) | 2,500 / Tape & Reel   |

| NCD57256DR2G   | SOIC-16 Narrow body (Pb-Free) | 2,500 / Tape & Reel   |

| NCV57256DR2G*  | SOIC-16 Narrow body (Pb-Free) | 2,500 / Tape & Reel   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

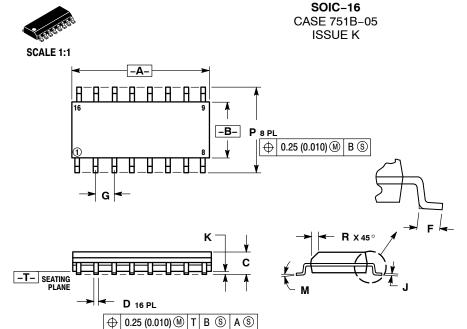

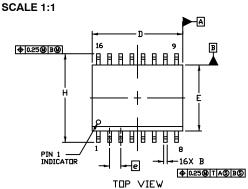

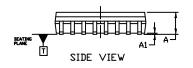

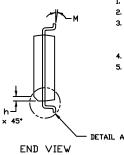

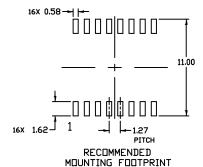

### **MECHANICAL CASE OUTLINE**

**DATE 29 DEC 2006**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- THE NOTION AND TOLETANOING FER ANSI'Y 14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- PHOI HUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR PROTRUSION

SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D

DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | METERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIM | MIN    | MAX    | MIN   | MAX   |

| Α   | 9.80   | 10.00  | 0.386 | 0.393 |

| В   | 3.80   | 4.00   | 0.150 | 0.157 |

| C   | 1.35   | 1.75   | 0.054 | 0.068 |

| D   | 0.35   | 0.49   | 0.014 | 0.019 |

| F   | 0.40   | 1.25   | 0.016 | 0.049 |

| G   | 1.27   | BSC    | 0.050 | BSC   |

| J   | 0.19   | 0.25   | 0.008 | 0.009 |

| K   | 0.10   | 0.25   | 0.004 | 0.009 |

| M   | 0°     | 7°     | 0°    | 7°    |

| P   | 5.80   | 6.20   | 0.229 | 0.244 |

| R   | 0.25   | 0.50   | 0.010 | 0.019 |

| STYLE 1: |               | STYLE 2: |               | STYLE 3: |                     | STYLE 4: |                |                |                                         |

|----------|---------------|----------|---------------|----------|---------------------|----------|----------------|----------------|-----------------------------------------|

| PIN 1.   | COLLECTOR     | PIN 1.   | CATHODE       | PIN 1.   | COLLECTOR, DYE #1   | PIN 1.   | COLLECTOR, DYE | #1             |                                         |

| 2.       | BASE          | 2.       | ANODE         | 2.       | BASE, #1            | 2.       | COLLECTOR, #1  |                |                                         |

| 3.       | EMITTER       | 3.       | NO CONNECTION | 3.       | EMITTER, #1         | 3.       | COLLECTOR, #2  |                |                                         |

| 4.       | NO CONNECTION | 4.       | CATHODE       | 4.       | COLLECTOR, #1       | 4.       | COLLECTOR, #2  |                |                                         |

| 5.       | EMITTER       | 5.       | CATHODE       | 5.       | COLLECTOR, #2       | 5.       | COLLECTOR, #3  |                |                                         |

| 6.       | BASE          | 6.       | NO CONNECTION | 6.       | BASE, #2            | 6.       | COLLECTOR, #3  |                |                                         |

| 7.       | COLLECTOR     | 7.       | ANODE         | 7.       | EMITTER, #2         | 7.       | COLLECTOR, #4  |                |                                         |

| 8.       | COLLECTOR     | 8.       | CATHODE       | 8.       | COLLECTOR, #2       | 8.       | COLLECTOR, #4  |                |                                         |

| 9.       | BASE          | 9.       | CATHODE       | 9.       | COLLECTOR, #3       | 9.       | BASE, #4       |                |                                         |

| 10.      | EMITTER       | 10.      | ANODE         | 10.      | BASE, #3            | 10.      | EMITTER, #4    |                |                                         |

| 11.      | NO CONNECTION | 11.      | NO CONNECTION | 11.      | EMITTER, #3         | 11.      | BASE, #3       |                |                                         |

| 12.      | EMITTER       | 12.      | CATHODE       | 12.      | COLLECTOR, #3       | 12.      | EMITTER, #3    |                |                                         |

| 13.      | BASE          | 13.      | CATHODE       | 13.      | COLLECTOR, #4       | 13.      | BASE, #2       | COL DEDING     | FOOTPRINT                               |

| 14.      | COLLECTOR     | 14.      | NO CONNECTION | 14.      | BASE, #4            | 14.      | EMITTER, #2    | SOLDERING      | 3 FOOTPRINT                             |

| 15.      | EMITTER       | 15.      | ANODE         | 15.      | EMITTER, #4         | 15.      | BASE, #1       |                | 8X                                      |

| 16.      | COLLECTOR     | 16.      | CATHODE       | 16.      | COLLECTOR, #4       | 16.      | EMITTER, #1    |                | 5.40 <del>→</del>                       |

|          |               |          |               |          |                     |          |                | 7              | ,.40                                    |

| STYLE 5: |               | STYLE 6: |               | STYLE 7: |                     |          |                |                | 16X 1.12 <                              |

| PIN 1.   | DRAIN, DYE #1 |          | CATHODE       | PIN 1.   | SOURCE N-CH         |          |                |                |                                         |

| 2.       | DRAIN, #1     |          | CATHODE       | 2.       | COMMON DRAIN (OUTPU | T)       |                | . 1            | 16                                      |

| 3.       | DRAIN, #2     | 3.       |               | 3.       | COMMON DRAIN (OUTPU |          |                | <b>↓ └──</b> · | " 🗀                                     |

| 4.       | DRAIN, #2     | 4.       | CATHODE       | 4.       | GATE P-CH           | .,       |                | <del>-</del> — |                                         |

| 5.       | DRAIN, #3     | 5.       | CATHODE       | 5.       | COMMON DRAIN (OUTPU | T)       | 16             | 5X <b>T</b>    |                                         |

| 6.       | DRAIN, #3     | 6.       | CATHODE       | 6.       | COMMON DRAIN (OUTPU |          | 0.5            | iii I          | · —                                     |

| 7.       | DRAIN, #4     | 7.       | CATHODE       | 7.       | COMMON DRAIN (OUTPU |          | 0.0            | 56             | 1                                       |

| 8.       | DRAIN, #4     | 8.       | CATHODE       | 8.       | SOURCE P-CH         | .,       |                |                |                                         |

| 9.       | GATE, #4      | 9.       | ANODE         | 9.       | SOURCE P-CH         |          |                |                |                                         |

| 10.      | SOURCE, #4    | 10.      | ANODE         | 10.      | COMMON DRAIN (OUTPU | T)       |                |                |                                         |

| 11.      | GATE, #3      | 11.      | ANODE         | 11.      | COMMON DRAIN (OUTPU |          |                |                |                                         |

| 12.      | SOURCE, #3    | 12.      | ANODE         | 12.      | COMMON DRAIN (OUTPU |          |                |                |                                         |

| 13.      | GATE, #2      | 13.      | ANODE         | 13.      | GATE N-CH           | ,        |                |                |                                         |

| 14.      | SOURCE, #2    | 14.      | ANODE         | 14.      | COMMON DRAIN (OUTPU | T)       |                |                | — VPITCH                                |

| 15.      | GATE, #1      | 15.      | ANODE         | 15.      | COMMON DRAIN (OUTPU |          |                |                | <u>+-+</u> -                            |

| 16.      | SOURCE, #1    | 16.      | ANODE         | 16.      | SOURCE N-CH         | •        |                |                |                                         |

|          | •             |          |               |          |                     |          |                | <b>□</b> 8     | 9 + - + -                               |

|          |               |          |               |          |                     |          |                | <b>—</b> -     | _ · · · · · · · · · · · · · · · · · · · |

|          |               |          |               |          |                     |          |                |                | DIMENSIONS, MILLIMETERS                 |

|          |               |          |               |          |                     |          |                |                | DIMENSIONS: MILLIMETERS                 |